Next: Inductive Interference

Up: Some SAT Benchmarks Visualised

Previous: Some SAT Benchmarks Visualised

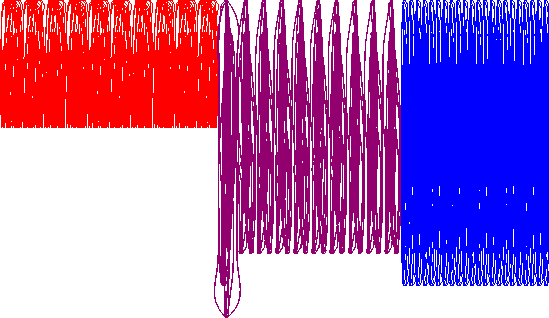

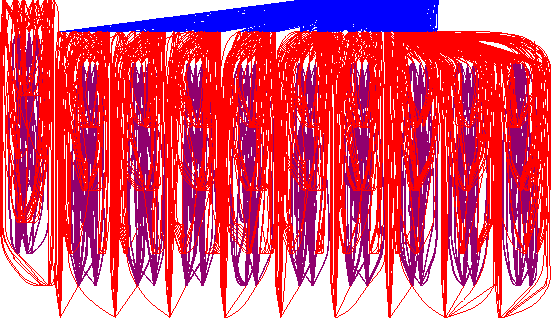

VLSI design of a 2 bit adder, from the Beijing benchmark suite, problem 2bitadd_10.cnf.

Under various graph interpretations, the hardware verification problems have significant

structural properties that suggests modularity and repetition. This suggests that there

maybe something for a search algorithm to exploit, possibly using partitioning and

unification techniques.

Figure 1:

2 Bit Adder, Cooccurrence of Variables

|

Figure 2:

2 Bit Adder, Cooccurrence of Literals

|

Figure 3:

2 Bit Adder, Basic Implicative Interpretation

|

Last modified: 2004-03-17

Andrew Slater