## SHIM and Its Applications

Xi Yang

A thesis submitted for the degree of Doctor of Philosophy The Australian National University

November 2019

© Xi Yang 2019

Except where otherwise indicated, this thesis is my own original work.

Xi Yang 1 November 2019

to Liang and Jayne.

### Acknowledgments

I am deeply indebted to my supervisors, Professors Steve Blackburn and Kathryn S. McKinley. They not only patiently supported me in addressing fundamental research problems. But more importantly, they showed me how to be a great teacher, a great parent, a great spouse, and a great humane person.

I am also greatly indebted to my hero, Huailin Chen, whose articles taught me the principles of computer systems and attracted me to the wonderful world of research and engineering.

Many people and organizations have provided generous support and assistance. I would like to thank Dan Luu and Martin Maas for promoting my research, and my managers, Michael Agnich, Charles Tripp, and Xin Xiang, for supporting me in finishing my thesis when I was working full time at TerrainData and Confluent. I also would like to thank my friends in our research lab, Yi, Kunshan, Tiejun, Ting, Ivan, Rifat, Vivek, and Luke, for their collaboration, support, and company. I would like to thank ANU and Google for providing scholarships, Microsoft Research for providing internships, and Centrelink for providing family benefits after my daughter was born

Lastly, I would like to thank my family for their love and support. For my parents, Yangai and Qiudong, who gave me considerable freedom when I grew up and supported me in pursuing my research. For my daughter, Jayne, whose regular sleep schedule provided precious working hours. And, most of all, for my loving wife, my best friend, and also my life mentor, Liang, whose constant support and invaluable life suggestions encouraged me. Now it is my turn to support her in pursuing her remarkable research.

## Abstract

Profiling is the most popular approach to diagnosing performance problems of computer systems. Profiling records run-time system behavior by monitoring software and hardware events either exhaustively or—because of high costs and strong observer effects—periodically. Sampling rates thus determine visibility: the higher the sample rates, the finer-grain behavior observable, and thus the better profilers can help developers analyze and address performance problems.

Unfortunately, the sample rates of current profilers are extremely low because of the perturbations generated by their sampling mechanisms. Consequently, current profilers cannot observe insightful fine-grain system behavior. Despite the gigahertz speeds of modern processors, sampling frequencies have been at a standstill—between 1 KHz and 100 KHz—to limit perturbation. This million-cycle gap between two sequential samples blinds profilers to fine-grain behaviors, thus missing root causes of performance problems and potential solutions.

My thesis is that by exploiting existing underutilized multicore hardware the sample rates of profilers can be increased by orders of magnitude, leading to new profiling approaches, new discoveries of insightful behavior, and new optimizations.

The insights and contributions of this thesis are: 1) We view computer systems as high-frequency signal generators. The high-frequency hardware and software signals that reflect fine-grain system behavior are observable in signal channels: performance counters and shared memory locations. We introduce SHIM, a new profiling approach that continuously samples signal channels at resolutions as fine as 15 cycles, which is three to five orders of magnitude finer than current sampling approaches. SHIM automatically filters out noisy samples to produce high-fidelity signals. 2) SHIM's high-frequency profiling enables a new approach to analyzing and controlling fine-grain system behaviors. We design TAILOR, a real-time latency controller for latency-critical web services. TAILOR uses a SHIM-based high-frequency profiler and an application-level network proxy to continuously monitor and promptly act on the system behaviors that are hazardous to request latency. 3) SHIM's fine-grain control of system components enables a new class of online profile-guided optimizations. We introduce Elfen, a Shim-based job scheduler that borrows cycles in short idle periods of latency-critical workloads for batch workloads. ELFEN improves CPU utilization significantly without interfering with latency-critical requests by monitoring status changes of latency-critical requests with SHIM, and taking real-time scheduling actions.

The history of science shows that an order of magnitude or more improvement in measurement fidelity leads to fundamental new discoveries. This thesis fundamentally alters which software and hardware signals are observable on existing systems, and demonstrates that observing these signals stimulates new optimization opportunities.

## Contents

| 2.2       Profiling Techniques         2.3       Problem Domain         2.4       Summary         3       SHIM         3.1       Introduction         3.2       Motivation         3.3       Design and Implementation         3.4       Observation Fidelity         3.4.1       Sampling Correction for Rate Metrics         3.4.2       Randomizing Sample Periods         3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signal Breakdown Analysis         3.6.3       Observing Hardware and Software Signals         3.6.4       Correlating Hardware and Software Signals         3.6.5       Negligible Overhead Fine-Grain Profiling         3.7.1       DVFS of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.8       Related Work                                                                                                                                | At | ostra | Ct                                       | ix |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|------------------------------------------|----|

| 1.2       Problem Statement         1.3       Insights and Contributions         1.4       Thesis Structure         2       Background         2.1       Profiling         2.1.1       Software and Hardware Events         2.1.2       Profiling Approaches         2.3       Profiling Techniques         2.3       Problem Domain         2.4       Summary         3       SHIM         3.1       Introduction         3.2       Motivation         3.3       Design and Implementation         3.4       Observation Fidelity         3.4.1       Sampling Correction for Rate Metrics         3.4.2       Randomizing Sample Periods         3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signal Breakdown Analysis         3.6.3       Observing Hardware and Software Signals         3.6.4       Correlating Hardware and Software Signals         3.6.5       Negligible Overhead Fine-Grain Profiling         3.7       DVFS of Garbage Collection Phases         3.7.1       DVFS of Garbage Co | 1  | Intr  | oduction                                 | 1  |

| 1.3       Insights and Contributions         1.4       Thesis Structure         2       Background         2.1       Profiling         2.1.1       Software and Hardware Events         2.1.2       Profiling Approaches         2.3       Problem Domain         2.4       Summary         2.5       Profiling Techniques         2.6       Problem Domain         2.7       Problem Domain         2.8       Summary         3       SHIM         3.1       Introduction         3.2       Motivation         3.3       Design and Implementation         3.4       Observation Fidelity         3.4.1       Sampling Correction for Rate Metrics         3.4.2       Randomizing Sample Periods         3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signals         3.6.3       Observing Hardware and Software Signals         3.6.4       Correlating Hardware and Software Signals         3.6.5       Negligible Overhead Fine-Grain Profiling         3.7.1       <                                |    | 1.1   | Motivation                               | 1  |

| 1.4 Thesis Structure <b>Background</b> 2.1 Profiling         2.1.1 Software and Hardware Events         2.1.2 Profiling Approaches         2.2 Profiling Techniques         2.3 Problem Domain         2.4 Summary         3 SHIM         3.1 Introduction         3.2 Motivation         3.3 Design and Implementation         3.4 Observation Fidelity         3.4.1 Sampling Correction for Rate Metrics         3.4.2 Randomizing Sample Periods         3.4.3 Other Observer Effects         3.5 Methodology         3.6 Evaluation         3.6.2 Software Signals         3.6.3 Observing Hardware Signals         3.6.4 Correlating Hardware and Software Signals         3.6.5 Negligible Overhead Fine-Grain Profiling         3.7.1 DVFS of Garbage Collection Phases         3.7.2 Hardware Prefetching of Garbage Collection Phases         3.7.2 Hardware Prefetching of Garbage Collection Phases                                                                                                                                                                                                                          |    | 1.2   | Problem Statement                        | 4  |

| 2       Background         2.1       Profiling         2.1.1       Software and Hardware Events         2.1.2       Profiling Approaches         2.2       Profiling Techniques         2.3       Problem Domain         2.4       Summary         3       SHIM         3.1       Introduction         3.2       Motivation         3.3       Design and Implementation         3.4       Observation Fidelity         3.4.1       Sampling Correction for Rate Metrics         3.4.2       Randomizing Sample Periods         3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signal Breakdown Analysis         3.6.3       Observing Hardware and Software Signals         3.6.4       Correlating Hardware and Software Signals         3.6.5       Negligible Overhead Fine-Grain Profiling         3.7       Case Studies         3.7.1       DVFS of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.8       Related Work                      |    | 1.3   | Insights and Contributions               | 4  |

| 2.1       Profiling         2.1.1       Software and Hardware Events         2.1.2       Profiling Approaches         2.3       Problem Domain         2.3       Problem Domain         2.4       Summary         3       SHIM         3.1       Introduction         3.2       Motivation         3.3       Design and Implementation         3.4       Observation Fidelity         3.4.1       Sampling Correction for Rate Metrics         3.4.2       Randomizing Sample Periods         3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signal Breakdown Analysis         3.6.3       Observing Hardware and Software Signals         3.6.4       Correlating Hardware and Software Signals         3.6.5       Negligible Overhead Fine-Grain Profiling         3.7       Case Studies         3.7.1       DVFS of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases                |    | 1.4   | 8                                        | 7  |

| 2.1.1       Software and Hardware Events         2.1.2       Profiling Approaches         2.2       Profiling Techniques         2.3       Problem Domain         2.4       Summary         2.4       Summary         3       SHIM         3.1       Introduction         3.2       Motivation         3.3       Design and Implementation         3.4       Observation Fidelity         3.4.1       Sampling Correction for Rate Metrics         3.4.2       Randomizing Sample Periods         3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signal Breakdown Analysis         3.6.3       Observing Hardware and Software Signals         3.6.4       Correlating Hardware and Software Signals         3.6.5       Negligible Overhead Fine-Grain Profiling         3.7       Case Studies         3.7.1       DVFS of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.8       Related Work                                                   | 2  | Bac   | kground                                  | 9  |

| 2.1.2Profiling Approaches2.2Profiling Techniques2.3Problem Domain2.4Summary3SHIM3.1Introduction3.2Motivation3.3Design and Implementation3.4Observation Fidelity3.4.1Sampling Correction for Rate Metrics3.4.2Randomizing Sample Periods3.4.3Other Observer Effects3.5Methodology3.6Evaluation3.6.1Observing Software Signals3.6.2Software Signal Breakdown Analysis3.6.3Observing Hardware and Software Signals3.6.4Correlating Hardware and Software Signals3.7Case Studies3.7.1DVFS of Garbage Collection Phases3.7.2Hardware Prefetching of Garbage Collection Phases3.8Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 2.1   | Profiling                                | 9  |

| 2.2       Profiling Techniques         2.3       Problem Domain         2.4       Summary         3       SHIM         3.1       Introduction         3.2       Motivation         3.3       Design and Implementation         3.4       Observation Fidelity         3.4.1       Sampling Correction for Rate Metrics         3.4.2       Randomizing Sample Periods         3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signal Breakdown Analysis         3.6.3       Observing Hardware and Software Signals         3.6.4       Correlating Hardware and Software Signals         3.7       Case Studies         3.7.1       DVFS of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases                                                                                                                       |    |       | 2.1.1 Software and Hardware Events       | 9  |

| <ul> <li>2.3 Problem Domain</li> <li>2.4 Summary</li> <li>3 SHIM</li> <li>3.1 Introduction</li> <li>3.2 Motivation</li> <li>3.3 Design and Implementation</li> <li>3.4 Observation Fidelity</li> <li>3.4.1 Sampling Correction for Rate Metrics</li> <li>3.4.2 Randomizing Sample Periods</li> <li>3.4.3 Other Observer Effects</li> <li>3.5 Methodology</li> <li>3.6 Evaluation</li> <li>3.6.1 Observing Software Signals</li> <li>3.6.2 Software Signal Breakdown Analysis</li> <li>3.6.3 Observing Hardware and Software Signals</li> <li>3.6.4 Correlating Hardware and Software Signals</li> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li> <li>3.7 Case Studies</li> <li>3.7.1 DVFS of Garbage Collection Phases</li> <li>3.8 Related Work</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |    |       | 2.1.2 Profiling Approaches               | 12 |

| <ul> <li>2.4 Summary</li> <li>3 SHIM</li> <li>3.1 Introduction</li> <li>3.2 Motivation</li> <li>3.3 Design and Implementation</li> <li>3.4 Observation Fidelity</li> <li>3.4.1 Sampling Correction for Rate Metrics</li> <li>3.4.2 Randomizing Sample Periods</li> <li>3.4.3 Other Observer Effects</li> <li>3.5 Methodology</li> <li>3.6 Evaluation</li> <li>3.6.1 Observing Software Signals</li> <li>3.6.2 Software Signal Breakdown Analysis</li> <li>3.6.3 Observing Hardware and Software Signals</li> <li>3.6.4 Correlating Hardware and Software Signals</li> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li> <li>3.7 Case Studies</li> <li>3.7.1 DVFS of Garbage Collection Phases</li> <li>3.7.2 Hardware Prefetching of Garbage Collection Phases</li> <li>3.8 Related Work</li> </ul>                                                                                                                                                                                                                                                                                                                                |    | 2.2   | Profiling Techniques                     | 15 |

| 3 SHIM         3.1 Introduction         3.2 Motivation         3.3 Design and Implementation         3.4 Observation Fidelity         3.4.1 Sampling Correction for Rate Metrics         3.4.2 Randomizing Sample Periods         3.4.3 Other Observer Effects         3.5 Methodology         3.6 Evaluation         3.6.2 Software Signals         3.6.3 Observing Hardware Signals         3.6.4 Correlating Hardware and Software Signals         3.6.5 Negligible Overhead Fine-Grain Profiling         3.7 Case Studies         3.7.1 DVFS of Garbage Collection Phases         3.7.2 Hardware Prefetching of Garbage Collection Phases         3.8 Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 2.3   | Problem Domain                           | 16 |

| <ul> <li>3.1 Introduction</li> <li>3.2 Motivation</li> <li>3.3 Design and Implementation</li> <li>3.4 Observation Fidelity</li> <li>3.4.1 Sampling Correction for Rate Metrics</li> <li>3.4.2 Randomizing Sample Periods</li> <li>3.4.3 Other Observer Effects</li> <li>3.5 Methodology</li> <li>3.6 Evaluation</li> <li>3.6.1 Observing Software Signals</li> <li>3.6.2 Software Signal Breakdown Analysis</li> <li>3.6.3 Observing Hardware and Software Signals</li> <li>3.6.4 Correlating Hardware and Software Signals</li> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li> <li>3.7 Case Studies</li> <li>3.7.1 DVFS of Garbage Collection Phases</li> <li>3.7.2 Hardware Prefetching of Garbage Collection Phases</li> <li>3.8 Related Work</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |    | 2.4   | Summary                                  | 17 |

| <ul> <li>3.2 Motivation</li> <li>3.3 Design and Implementation</li> <li>3.4 Observation Fidelity</li> <li>3.4.1 Sampling Correction for Rate Metrics</li> <li>3.4.2 Randomizing Sample Periods</li> <li>3.4.3 Other Observer Effects</li> <li>3.5 Methodology</li> <li>3.6 Evaluation</li> <li>3.6.1 Observing Software Signals</li> <li>3.6.2 Software Signal Breakdown Analysis</li> <li>3.6.3 Observing Hardware Signals</li> <li>3.6.4 Correlating Hardware and Software Signals</li> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li> <li>3.7 Case Studies</li> <li>3.7.1 DVFS of Garbage Collection Phases</li> <li>3.8 Related Work</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  | SHI   | Μ                                        | 19 |

| <ul> <li>3.3 Design and Implementation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    | 3.1   | Introduction                             | 19 |

| <ul> <li>3.4 Observation Fidelity</li> <li>3.4.1 Sampling Correction for Rate Metrics</li> <li>3.4.2 Randomizing Sample Periods</li> <li>3.4.3 Other Observer Effects</li> <li>3.5 Methodology</li> <li>3.6 Evaluation</li> <li>3.6.1 Observing Software Signals</li> <li>3.6.2 Software Signal Breakdown Analysis</li> <li>3.6.3 Observing Hardware Signals</li> <li>3.6.4 Correlating Hardware Signals</li> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li> <li>3.7 Case Studies</li> <li>3.7.1 DVFS of Garbage Collection Phases</li> <li>3.7.2 Hardware Prefetching of Garbage Collection Phases</li> <li>3.8 Related Work</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 3.2   | Motivation                               | 22 |

| <ul> <li>3.4 Observation Fidelity</li> <li>3.4.1 Sampling Correction for Rate Metrics</li> <li>3.4.2 Randomizing Sample Periods</li> <li>3.4.3 Other Observer Effects</li> <li>3.5 Methodology</li> <li>3.6 Evaluation</li> <li>3.6.1 Observing Software Signals</li> <li>3.6.2 Software Signal Breakdown Analysis</li> <li>3.6.3 Observing Hardware Signals</li> <li>3.6.4 Correlating Hardware and Software Signals</li> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li> <li>3.7 Case Studies</li> <li>3.7.1 DVFS of Garbage Collection Phases</li> <li>3.7.2 Hardware Prefetching of Garbage Collection Phases</li> <li>3.8 Related Work</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 3.3   | Design and Implementation                | 25 |

| <ul> <li>3.4.1 Sampling Correction for Rate Metrics</li> <li>3.4.2 Randomizing Sample Periods</li> <li>3.4.3 Other Observer Effects</li> <li>3.5 Methodology</li> <li>3.6 Evaluation</li> <li>3.6.1 Observing Software Signals</li> <li>3.6.2 Software Signal Breakdown Analysis</li> <li>3.6.3 Observing Hardware Signals</li> <li>3.6.4 Correlating Hardware and Software Signals</li> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li> <li>3.7 Case Studies</li> <li>3.7.1 DVFS of Garbage Collection Phases</li> <li>3.7.2 Hardware Prefetching of Garbage Collection Phases</li> <li>3.8 Related Work</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 3.4   |                                          | 28 |

| <ul> <li>3.4.2 Randomizing Sample Periods</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |       | -                                        | 28 |

| 3.4.3       Other Observer Effects         3.5       Methodology         3.6       Evaluation         3.6.1       Observing Software Signals         3.6.2       Software Signal Breakdown Analysis         3.6.3       Observing Hardware Signals         3.6.4       Correlating Hardware and Software Signals         3.6.5       Negligible Overhead Fine-Grain Profiling         3.7       Case Studies         3.7.1       DVFS of Garbage Collection Phases         3.7.2       Hardware Prefetching of Garbage Collection Phases         3.8       Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       | 1 0                                      | 31 |

| <ul> <li>3.6 Evaluation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       | 3.4.3 Other Observer Effects             | 31 |

| <ul> <li>3.6 Evaluation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 3.5   | Methodology                              | 31 |

| <ul> <li>3.6.2 Software Signal Breakdown Analysis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 3.6   | Evaluation                               | 33 |

| <ul> <li>3.6.2 Software Signal Breakdown Analysis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       | 3.6.1 Observing Software Signals         | 34 |

| <ul> <li>3.6.3 Observing Hardware Signals</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |       | 3.6.2 Software Signal Breakdown Analysis | 36 |

| <ul> <li>3.6.4 Correlating Hardware and Software Signals</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       |                                          | 37 |

| <ul> <li>3.6.5 Negligible Overhead Fine-Grain Profiling</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       |                                          | 40 |

| <ul> <li>3.7 Case Studies</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |       |                                          | 40 |

| <ul> <li>3.7.1 DVFS of Garbage Collection Phases</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 3.7   |                                          | 40 |

| <ul><li>3.7.2 Hardware Prefetching of Garbage Collection Phases</li><li>3.8 Related Work</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       |                                          | 41 |

| 3.8 Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       |                                          | 42 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 3.8   | 8 0                                      | 47 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 3.9   |                                          | 50 |

| 4  | Tail       | or                                           | 51       |

|----|------------|----------------------------------------------|----------|

|    | 4.1        | Introduction                                 | 51       |

|    | 4.2        | TAILOR Design and Implementation             | 54       |

|    |            | 4.2.1 TALECHAIN Events                       |          |

|    |            | 4.2.2 TAILOR Profiler and Proxy              | 57       |

|    |            | 4.2.3 Local-Node Redundancy                  | 61       |

|    | 4.3        | System Setup                                 | 64       |

|    | 4.4        | Hazardous System Behaviors and Optimizations | 65       |

|    | 4.5        | Related Work                                 | 70       |

|    | 4.6        | Summary                                      | 73       |

| 5  | Elfe       |                                              | 75       |

| 3  | 5.1        | Introduction                                 | 75       |

|    | 5.1<br>5.2 | Background and Motivation                    |          |

|    | 5.2<br>5.3 | 0                                            | 70<br>84 |

|    | 5.5        | ELFEN Design and Implementation5.3.1Nanonap  | 85       |

|    |            | 1                                            | 86       |

|    |            |                                              | 00<br>88 |

|    |            | 0 0 0                                        |          |

|    | <b>F</b> 4 | 5.3.4 Elfen Scheduling                       |          |

|    | 5.4        | Methodology                                  |          |

|    | 5.5        |                                              |          |

|    | 5.6        | Related Work                                 |          |

|    | 5.7        | Summary                                      | 101      |

| 6  | Con        | clusion                                      | 103      |

|    | 6.1        | Future Work                                  | 104      |

|    |            | 6.1.1 Distributed High-Frequency Profiling   | 104      |

|    |            | 6.1.2 A Profiling Core                       | 104      |

|    |            | 6.1.3 System Signal Processing               | 104      |

|    | 6.2        | Final Words                                  | 105      |

| Bi | bliog      | raphy                                        | 107      |

# **List of Figures**

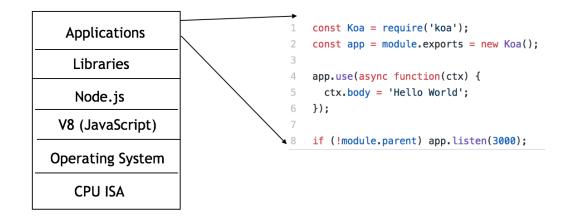

| 1.1 | Leveraging rich abstractions makes it possible to craft a simple http<br>server in a few lines of JavaScript code.                                                                                                                                                                                                                                                                                                                                                                                                   | 2        |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

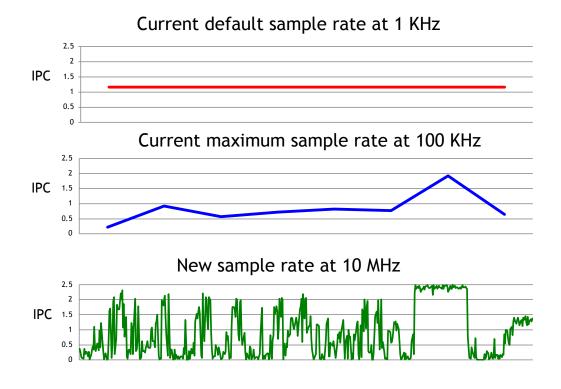

| 1.2 | IPC timeline for Lusearch. Sampling with 10 MHz exposes behavior unseen by existing profilers (red, blue).                                                                                                                                                                                                                                                                                                                                                                                                           | 3        |

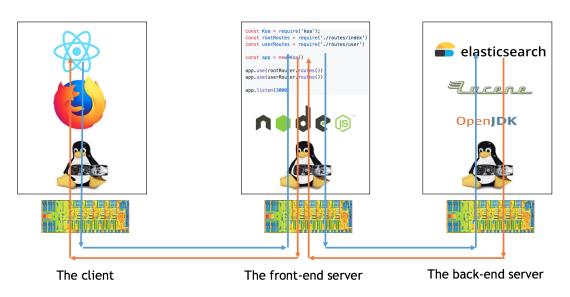

| 1.3 | A simple web request crosses layers of complex systems in a few mil-<br>liseconds                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4        |

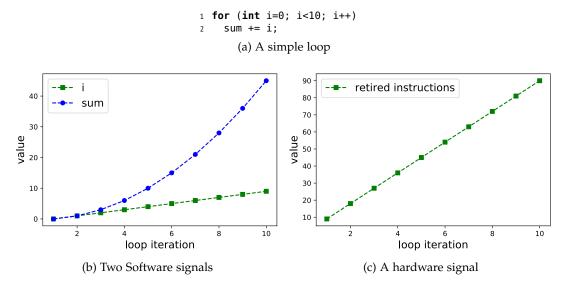

| 2.1 | Computer systems generate software and hardware signals                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10       |

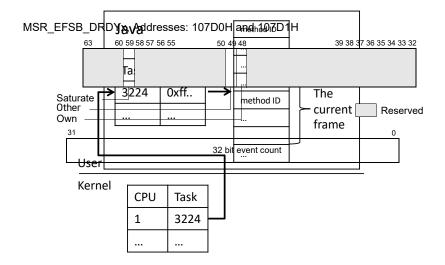

| 2.2 | Locating signal channels of current-method-id events                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11       |

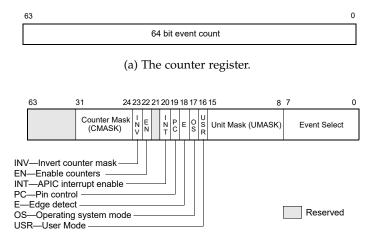

| 2.3 | The Intel performance counter specification [Intel, 2019]                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11       |

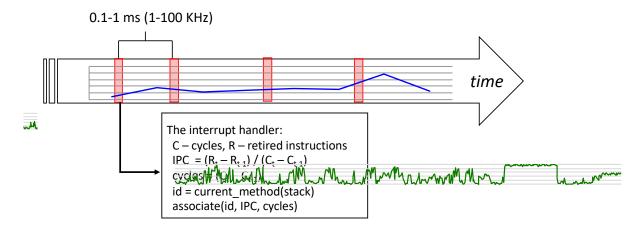

| 2.4 | Three sampling approaches: instrumentation, interrupt-driven sam-                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10       |

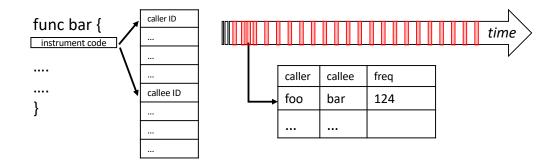

| 2.5 | pling, and direct observation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13<br>14 |

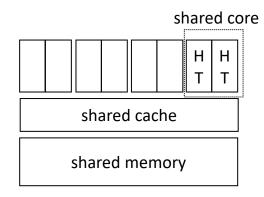

| 2.5 | Shared hardware resources can be shared charmers                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14       |

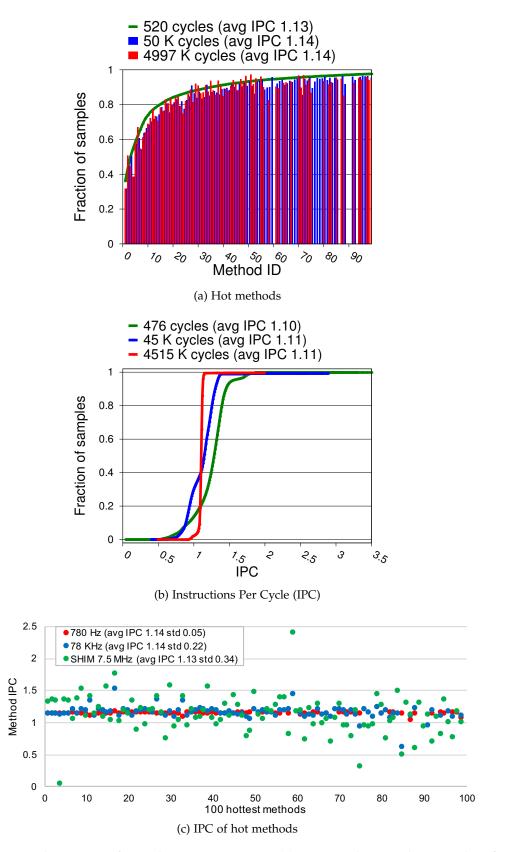

| 3.1 | The impact of sample rate on lusearch. (a) Varying the sample rates identifies similar hot methods. The green curve is the cumulative frequency distribution of samples at high frequency. Medium (red) and low (blue) frequency sampling cumulative frequency histograms are permuted to align with the green. (b) Sample rate significantly affects measures such as IPC. (c) Sample rate significantly affects IPC of hot methods. Each bar shows average IPC for a given hot method at one of three sample rates | 23       |

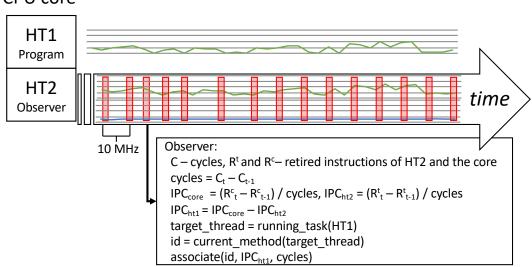

| 3.2 | Sнім observer loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27       |

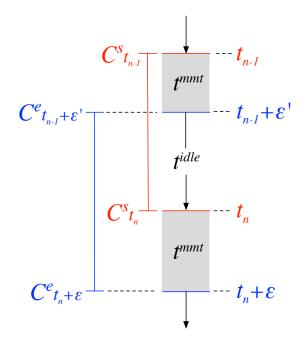

| 3.3 | Four clock readings ensure fidelity of rate measurements. Grey regions depict two measurements, $t_n^{mmt}$ and $t_{n-1}^{mmt}$ , in which SHIM reads all counters. The sample period is, $C^s$ (red) to $C^e$ (blue). If the ratio of red and blue periods is one, then $t_n^{mmt} = t_{n-1}^{mmt}$ and SHIM does not induce noise. DTE discards noisy measurements of rate metrics based on this ratio.                                                                                                            | 28       |

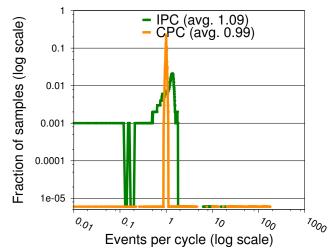

| 3.4 | DTE filtering on SMT keeps samples for which ground truth CPC is $1.\pm0.01$ , eliminating impossible IPC values. At small sample periods, DTE discards over half the samples. At sample periods >2000, DTE                                                                                                                                                                                                                                                                                                          |          |

|     | discards 10% or fewer samples.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 30       |

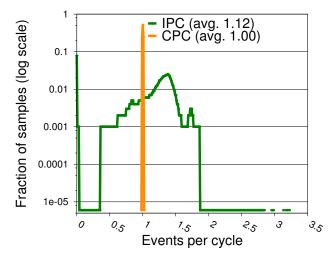

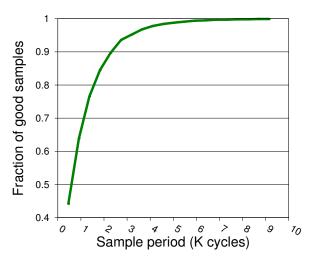

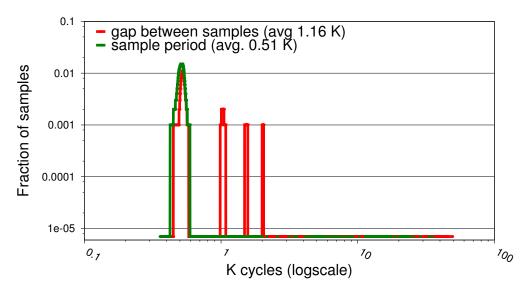

| 3.5 | SHIM has large variation in sample period and between samples with DTE filtering. The green curve shows variation in the period of good samples. The red curve shows variation in the period between consec-                                                                                                                                                                                                                                                                                                         |          |

|     | utive good samples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32       |

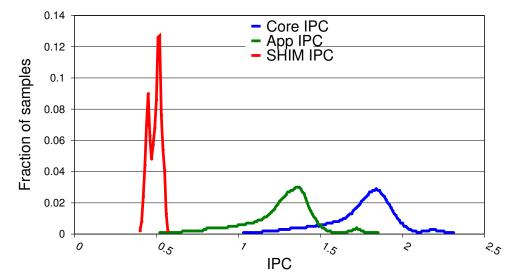

| 3.6  | SHIM SMT observer effect on IPC for 476 cycle sample period with lusearch. The green curve shows lusearch IPC, red shows SHIM's IPC,             |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | and blue shows IPC for the whole core                                                                                                            | 32 |

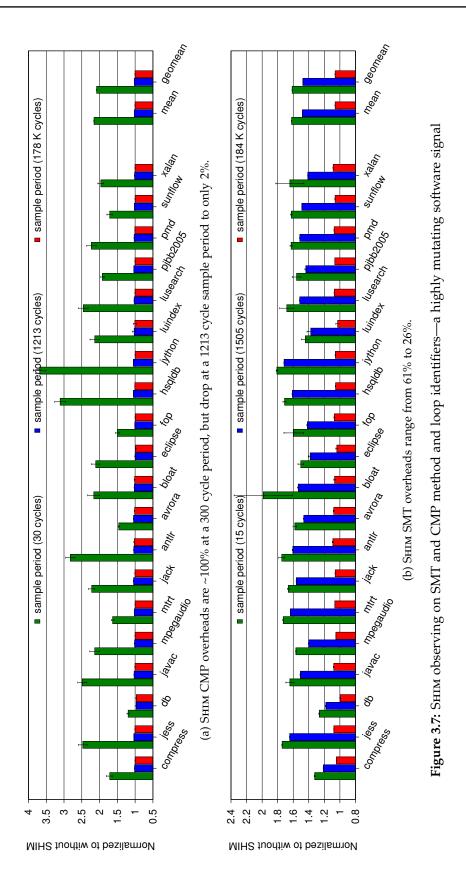

| 3.7  | SHIM observing on SMT and CMP method and loop identifiers—a                                                                                      |    |

|      | highly mutating software signal                                                                                                                  | 35 |

| 3.8  | Microbenchmarks explore software overheads                                                                                                       | 37 |

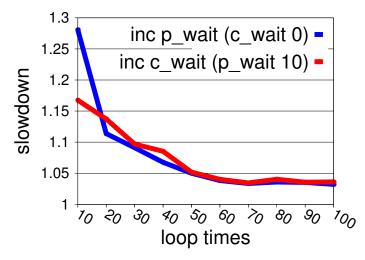

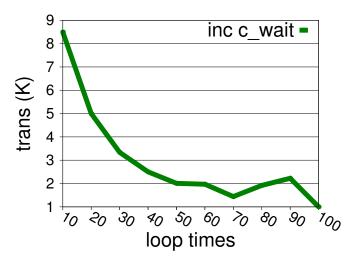

| 3.9  | CMP overheads. Write-invalidates induce observer effects and over-<br>heads. Increasing the producer or consumer periods drop the over-          |    |

|      | heads to $< 5\%$ .                                                                                                                               | 38 |

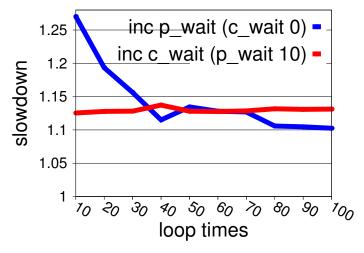

| 3.10 | SMT overheads. SMT observer effects are highest as a function of producer, but then relatively constant at $\sim 10\%$ .                         | 38 |

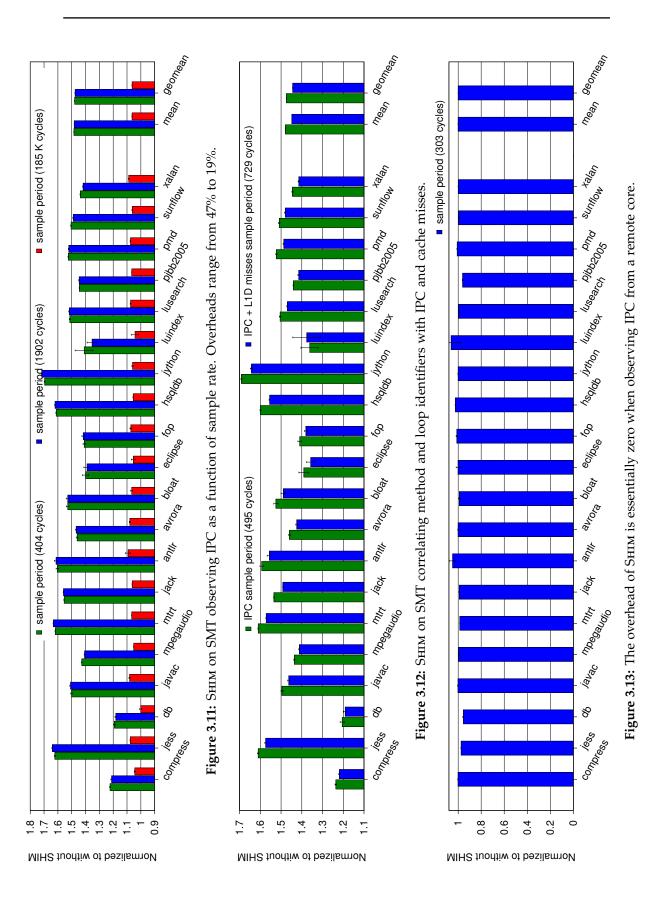

| 3.11 | SHIM on SMT observing IPC as a function of sample rate. Overheads range from 47% to 19%.                                                         | 39 |

| 3.12 | SHIM on SMT correlating method and loop identifiers with IPC and                                                                                 |    |

|      | cache misses.                                                                                                                                    | 39 |

| 3.13 | The overhead of SHIM is essentially zero when observing IPC from a                                                                               |    |

|      | remote core.                                                                                                                                     | 39 |

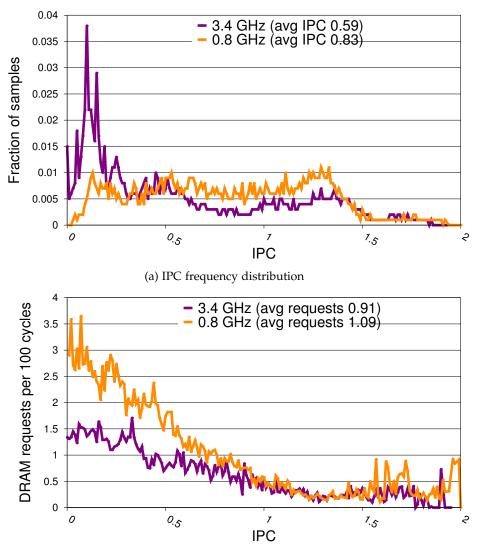

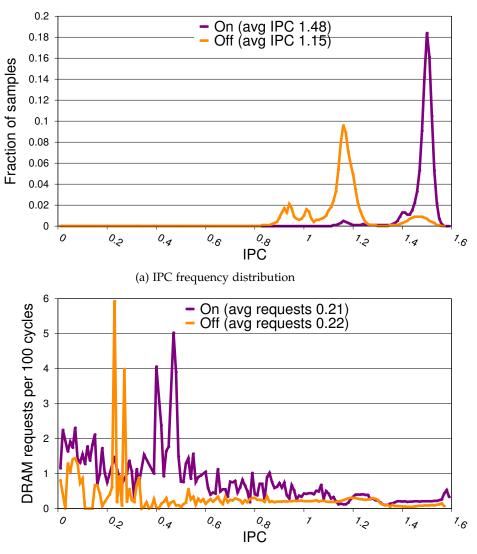

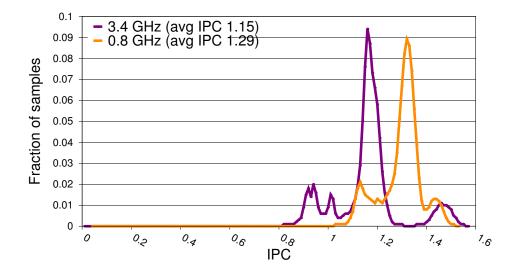

| 3.14 | DVFS effect at 3.4 and 0.8 GHz on IPC and memory bandwidth for                                                                                   |    |

|      | stacks (poor locality).                                                                                                                          | 43 |

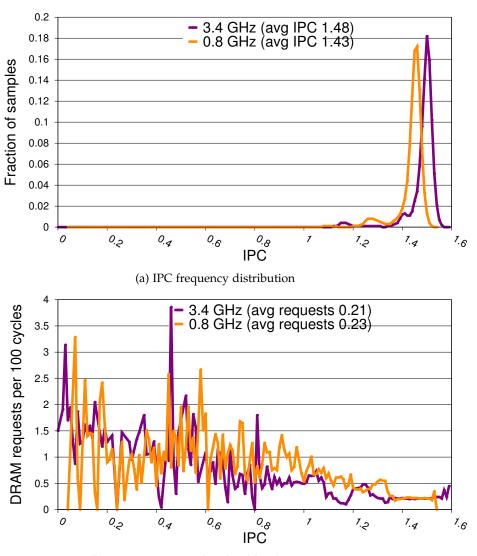

| 3.15 | DVFS effect at 3.4 and 0.8 GHz on IPC and memory bandwidth for                                                                                   |    |

|      | globals (good locality).                                                                                                                         | 44 |

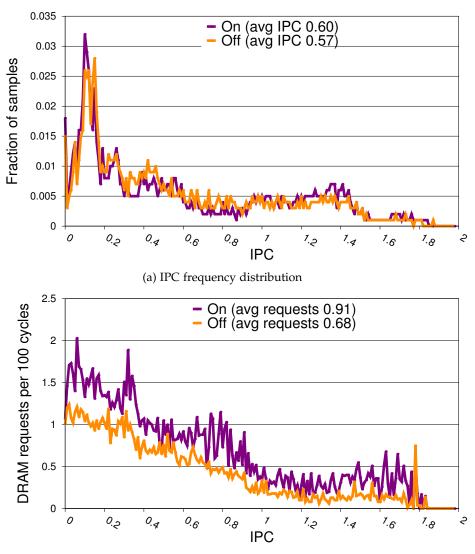

| 3.16 | Prefetching effect (on/off) on IPC and memory bandwidth for stacks (poor locality).                                                              | 45 |

| 3.17 | Prefetching effect (on/off) on IPC and memory bandwidth for globals (good locality).                                                             | 46 |

| 3.18 | DVFS effect on IPC for globals with prefetching off                                                                                              | 47 |

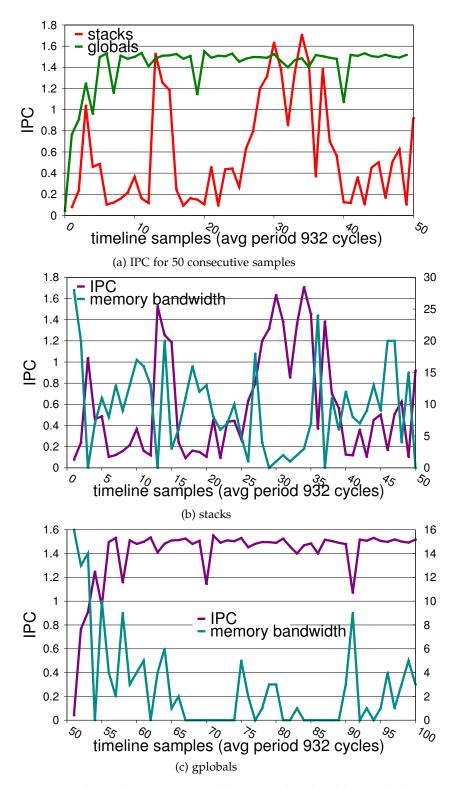

| 3.19 | Strong correlation between IPC and memory bandwidth revealed in                                                                                  |    |

|      | time line series for stacks and globals                                                                                                          | 48 |

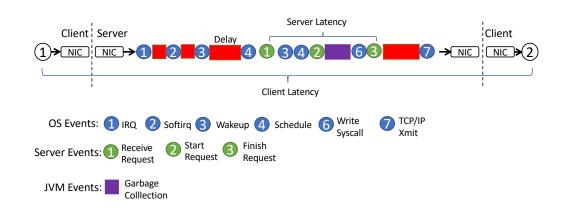

| 4.1  | The life of a latency-critical request. Notice that the client-observed latency (bottom) is very different to the server-observed latency (top). | 52 |

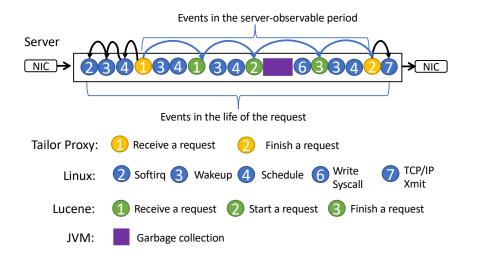

| 4.2  | A timeline of TALECHAIN events shows the behavior of requests                                                                                    |    |

| 4.3  | TAILOR instruments Linux to generate the kernel wakeup event into                                                                                | 50 |

| 4.5  | the software channel.                                                                                                                            | 57 |

| 4.4  | TAILOR creates software channels for the operating system, the JVMs,                                                                             | 01 |

| 1.1  | the proxy, and Lucene search servers.                                                                                                            | 58 |

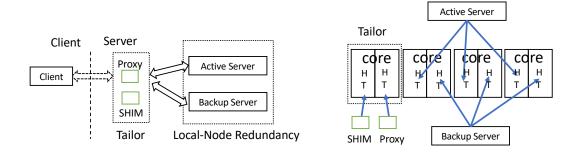

| 4.5  | The architecture of TAILOR                                                                                                                       | 59 |

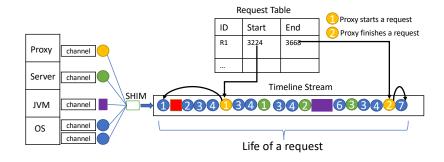

| 4.6  | The SHIM profiler continuously records new TALECHAIN events from                                                                                 |    |

|      | software channels into the timeline stream and takes preprogrammed actions for certain events.                                                   | 60 |

| 4.7  | The proxy forwards requests and responses between clients and the active and backup servers, maintains the request table, and analyzes           | 00 |

|      | slow requests.                                                                                                                                   | 62 |

|      |                                                                                                                                                  |    |

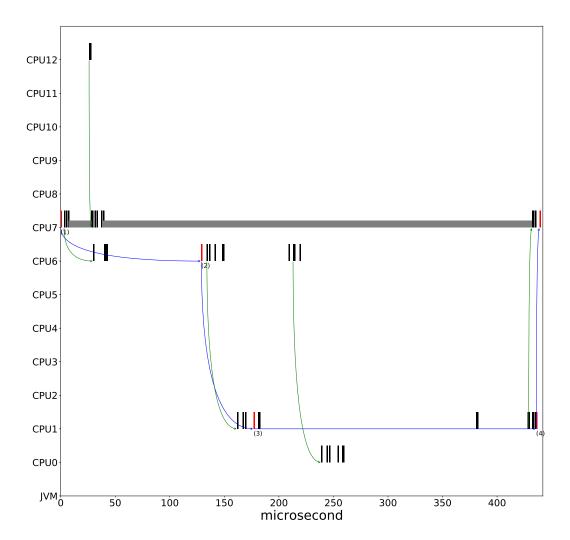

| 4.8                                                       | TAILOR presents a timeline view of a Lucene request. Each bar represents one TALECHAIN event. The red bars mark the five stages of                                                                                                                     |                                      |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|                                                           | processing requests: the proxy receives the request, then the Lucene                                                                                                                                                                                   |                                      |

|                                                           | coordinator task receives the request, the Lucene worker starts to pro-                                                                                                                                                                                |                                      |

|                                                           | cess the request, the Lucene worker finishes the request, and finally the                                                                                                                                                                              |                                      |

|                                                           | proxy finishes the request. The blue arrows show the request flow of                                                                                                                                                                                   |                                      |

|                                                           | these five stages, while the green arrows show wake-up chains pointing                                                                                                                                                                                 |                                      |

|                                                           | from wakeup events to their corresponding schedule events                                                                                                                                                                                              | 63                                   |

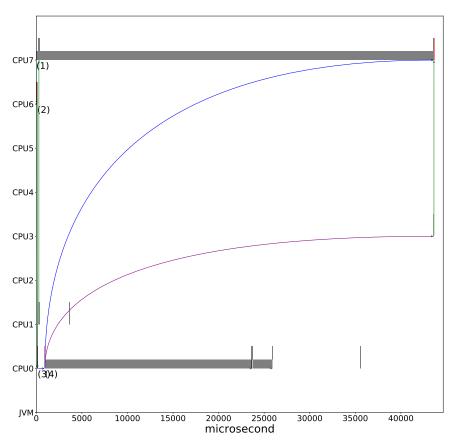

| 4.9                                                       | The SHIM profiler mitigates the impact of JVM pauses by sending                                                                                                                                                                                        |                                      |

| 1.,                                                       | hedged requests after detecting hazardous events.                                                                                                                                                                                                      | 64                                   |

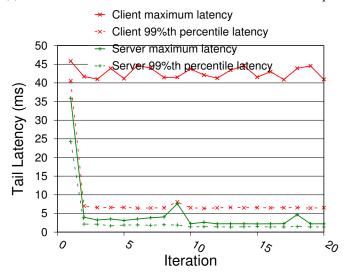

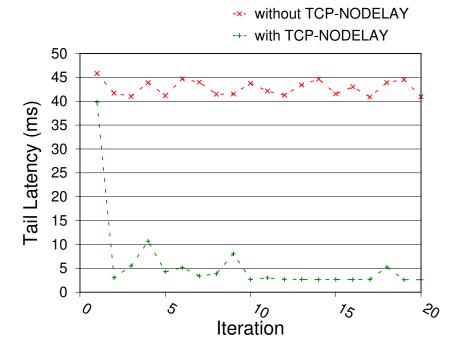

| 4 10                                                      | The tail latency of sending 1000 requests in 20 iterations at 1000 QPS.                                                                                                                                                                                |                                      |

|                                                           | The operating system buffers the request response. Disabling the TCP                                                                                                                                                                                   | . 00                                 |

| <b>T</b> •11                                              | Nagle algorithm avoids the hazardous behavior.                                                                                                                                                                                                         | . 68                                 |

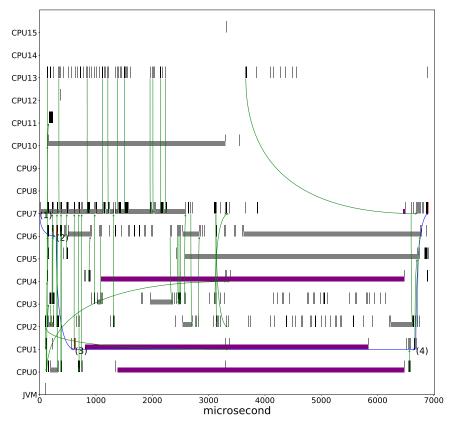

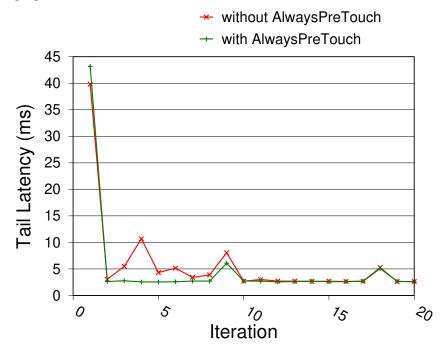

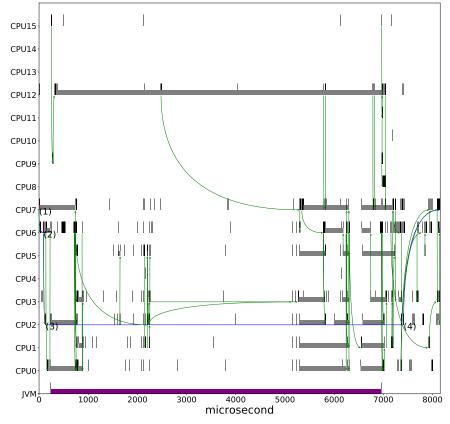

| 4 1 2                                                     | Extremely long page faults after the deep sleep slow down requests.                                                                                                                                                                                    | . 00                                 |

| <b>T</b> .12                                              | Pre-touching the JVM heap avoids triggering the hazardous behavior,                                                                                                                                                                                    |                                      |

|                                                           | reducing the client-side tail latencies of iterations 3-8 under 3 ms con-                                                                                                                                                                              |                                      |

|                                                           | sistently. Notice that other peaks caused by JVM pauses have not been                                                                                                                                                                                  |                                      |

|                                                           | addressed yet.                                                                                                                                                                                                                                         | . 69                                 |

| 4 13                                                      | JVM pauses caused by class loading and garbage collection affect re-                                                                                                                                                                                   | . 07                                 |

| 1.10                                                      | quest latency.                                                                                                                                                                                                                                         | . 71                                 |

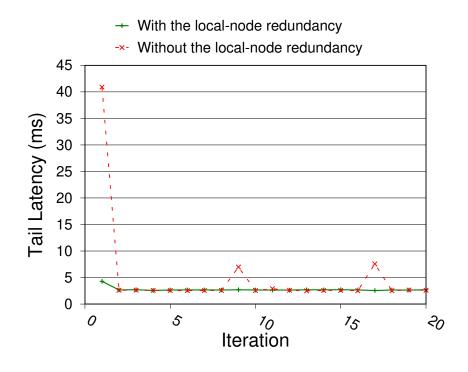

| 4 1 4                                                     | TAILOR reduces the maximum client-side tail latency by mitigating the                                                                                                                                                                                  | , , 1                                |

| 1.1 1                                                     | impact of JVM pauses with the local-node redundancy.                                                                                                                                                                                                   | . 72                                 |

|                                                           | inipact of joint paubeb with the focul flowe requirediney.                                                                                                                                                                                             |                                      |

|                                                           |                                                                                                                                                                                                                                                        |                                      |

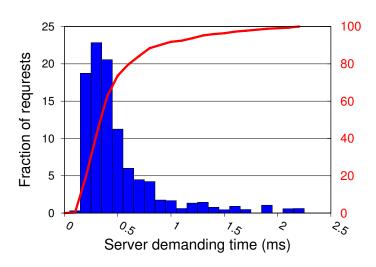

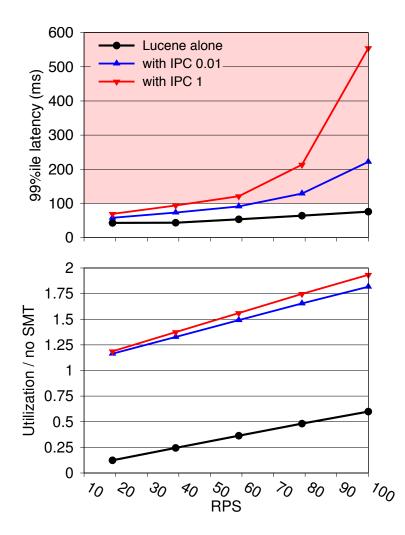

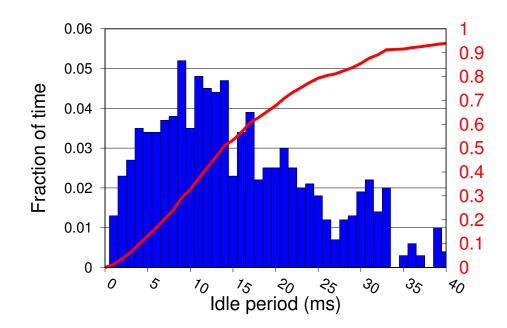

| 5.1                                                       | Highly variable demand is typical for latency-critical workloads.                                                                                                                                                                                      |                                      |

| 5.1                                                       |                                                                                                                                                                                                                                                        |                                      |

| 5.1                                                       | Highly variable demand is typical for latency-critical workloads.                                                                                                                                                                                      |                                      |

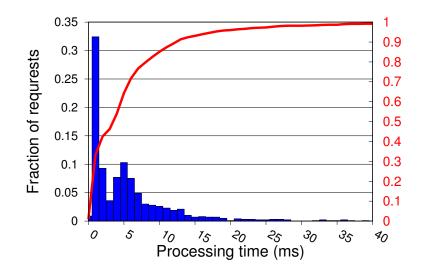

| 5.1                                                       | <b>Highly variable demand is typical for latency-critical workloads.</b><br>Lucene demand distribution with request processing time on x-axis in                                                                                                       | . 79                                 |

| 5.1<br>5.2                                                | <b>Highly variable demand is typical for latency-critical workloads.</b><br>Lucene demand distribution with request processing time on x-axis in 1 ms buckets, fraction of total on left y-axis, and cumulative distribution                           |                                      |

|                                                           | <b>Highly variable demand is typical for latency-critical workloads.</b><br>Lucene demand distribution with request processing time on x-axis in 1 ms buckets, fraction of total on left y-axis, and cumulative distribution red line on right y-axis. |                                      |

|                                                           | <b>Highly variable demand is typical for latency-critical workloads.</b><br>Lucene demand distribution with request processing time on x-axis in 1 ms buckets, fraction of total on left y-axis, and cumulative distribution red line on right y-axis  | . 79                                 |

|                                                           | <b>Highly variable demand is typical for latency-critical workloads.</b><br>Lucene demand distribution with request processing time on x-axis in 1 ms buckets, fraction of total on left y-axis, and cumulative distribution red line on right y-axis  | . 79                                 |

| 5.2                                                       | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79                                 |

| 5.2                                                       | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80                         |

| 5.2                                                       | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80                         |

| 5.2<br>5.3                                                | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80                         |

| 5.2<br>5.3                                                | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81                 |

| 5.2<br>5.3                                                | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81                 |

| 5.2<br>5.3<br>5.4                                         | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81                 |

| 5.2<br>5.3<br>5.4                                         | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81                 |

| 5.2<br>5.3<br>5.4                                         | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81<br>. 82         |

| 5.2<br>5.3<br>5.4                                         | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81<br>. 82         |

| 5.2<br>5.3<br>5.4                                         | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81<br>. 82<br>. 83 |

| <ul><li>5.2</li><li>5.3</li><li>5.4</li><li>5.5</li></ul> | Highly variable demand is typical for latency-critical workloads.<br>Lucene demand distribution with request processing time on x-axis in<br>1 ms buckets, fraction of total on left y-axis, and cumulative distribution<br>red line on right y-axis   | . 79<br>. 80<br>. 81<br>. 82<br>. 83 |

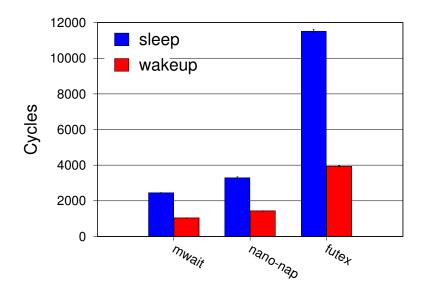

| 5.8  | Time to sleep and wake-up SMT partner lanes.                          | 88 |

|------|-----------------------------------------------------------------------|----|

| 5.9  | The pseudocode of four scheduling policies (the borrow idle policy    |    |

|      | and the fixed budget policy).                                         | 90 |

| 5.9  | The pseudocode of four scheduling policies (the refresh budget policy |    |

|      | and the dynamic refresh policy)                                       | 91 |

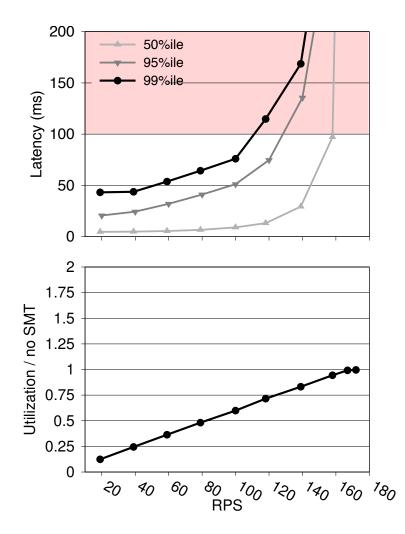

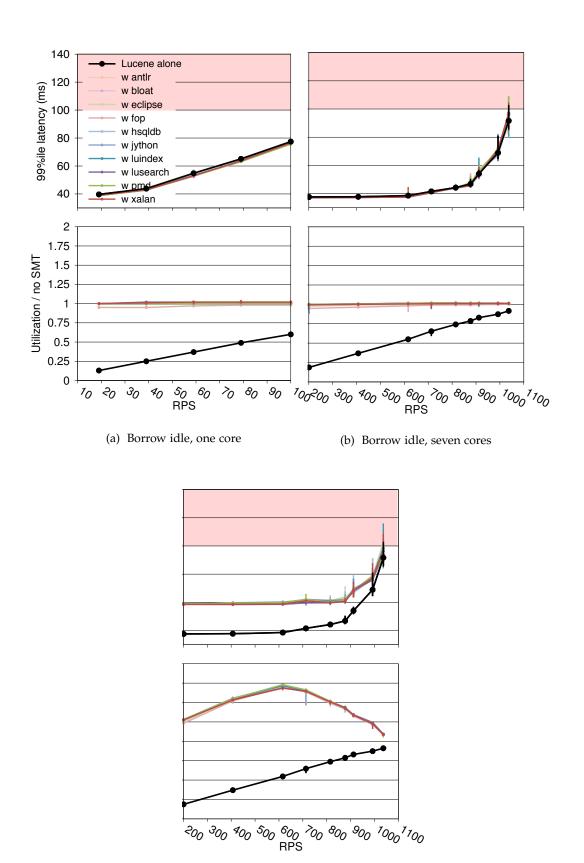

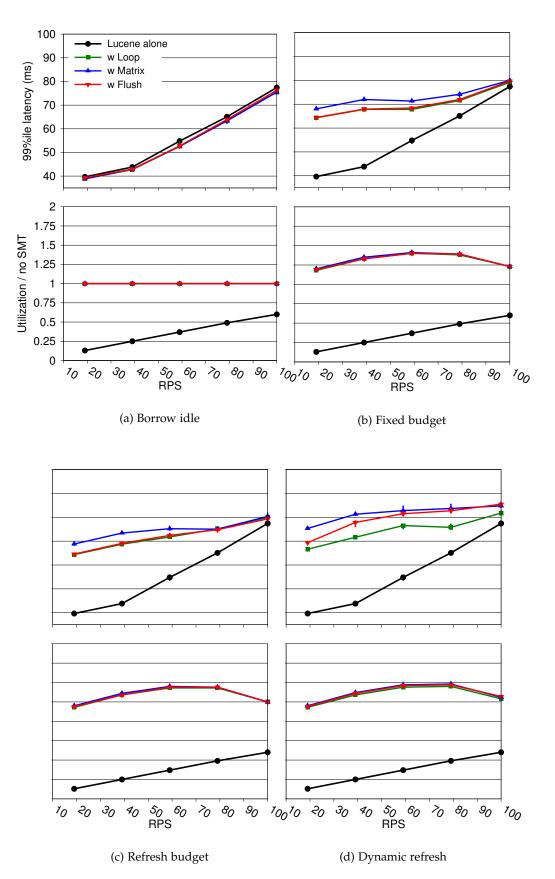

| 5.10 | 99th percentile latency (top) and utilization (bottom) for Lucene co- |    |

|      | running with DaCapo batch workloads                                   | 95 |

| 5.11 | 99th percentile latency (top) and utilization (bottom) for Lucene co- |    |

|      | running with C microbenchmarks under four ELFEN policies on a single  |    |

|      | two-way SMT core.                                                     | 97 |

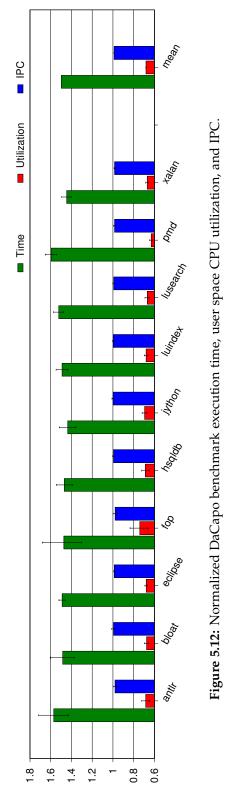

| 5.12 | Normalized DaCapo benchmark execution time, user space CPU uti-       |    |

|      | lization, and IPC.                                                    | 99 |

## List of Tables

### Introduction

In this dissertation, we focus on *general purpose sampling-based profilers* that observe both software and hardware behavior by sampling hardware and software events on existing hardware platforms.

Specifically, we addresse the challenge of designing new high-frequency highfidelity profilers on existing hardware platforms, discovering insightful fine-grain system behaviors with new profilers, and designing a new class of profile-guided optimizations.

#### 1.1 Motivation