# VLSI Implementation of Efficient Video Processor for Worldwide TV-OUT

Sungmok Lee<sup>#1</sup>, Jeonguk Im<sup>#2</sup>, Jingun Song<sup>#3</sup>, Joohyun Kim<sup>\*4</sup>, Bongsoon Kang<sup>#5</sup>

<sup>#</sup>Department of Electronics Engineering, Dong-A University

840 Hadan-dong, Saha-gu, Busan, Korea

{<sup>1</sup>jackal13, <sup>2</sup>hammer18, <sup>3</sup>sjg123}@didec.donga.ac.kr

<sup>5</sup>bongsoon@dau.ac.kr

\* SAMSUNG Electro-Mechanics Co. Ltd

314 Maetan-3-dong, Yeong-tong-gu, Suwon, Korea

<sup>4</sup>joohyunkim@samsung.com

Abstract-This paper presents the integrated architecture of worldwide TV-OUT video processor that can be used throughout the world. SECAM, one of the color TV standards, uses FM modulation by contrast with NTSC and PAL. So SECAM must have an anti-cloche filter, but the filter recommended by standard is not easy to implement the hardware due to the sharpness of the frequency response. We modified characteristic of anti-cloche filter and modulation method so as to be identical with a result required by standard so that it is easy to design the hardware. The hardwired TV-out function is requisite since portable devices are widely getting popularized. Therefore, we propose TV-out video processor that has low hardware complexity, which can be applied to various portable multimedia applications.

## I. INTRODUCTION

To transfer color images through a broadcasting channel, current television broadcasting standards use Composite Video Baseband Signals (CVBS) such as National Television Standards Committee (NTSC), Phase Alternation Line (PAL), and Sequentiel Couleur Avec Memoire or Sequential Color with Memory (SECAM). The TV-OUT video processor takes component video signals (e.g., RGB or YCbCr) and encodes these into the CVBS. The RGB represents red, green and blue. The YCbCr represents luminance(Y) corresponding to brightness and chrominance components (Cb, Cr) corres ponding to hue and saturation. The International Telecomm unication Union (ITU) has established the standard format of the CVBS, which is ITU-R BT.470 [1]. Table 1 summarizes the formats and their characteristics. The proposed video processor supports all formats in Table 1. AM means amplitude modulation and FM is frequency modulation in Table 1.

Formerly, DVD-players, digital camcorders, video game consoles and etc, needed the TV-OUT function, but the newly debuted devices such as a Potable Multimedia Player (PMP), a laptop computer, a camera phone and etc, commonly require TV-OUT function as well. A video processing technology for TV-OUT is not the latest technology but it has widely being used for multimedia devices. The TV-OUT processor must support all standards in Table 1 to cover the worldwide market. Therefore, we propose a TV-OUT video processor using a

compact architecture to reduce production costs and to cover worldwide TV-OUT formats.

| SUMMARY OF WORLDWIDE COLOR TV SYSTEM |                      |                               |  |  |

|--------------------------------------|----------------------|-------------------------------|--|--|

| Output formats                       | Modulation<br>Method | Sub-carrier<br>frequency(MHz) |  |  |

| M, J/NTSC                            | AM                   | 3.5795454545                  |  |  |

| 4.43/NTSC                            | AM                   | 4.43361875                    |  |  |

| M/PAL                                | AM                   | 3.5756118881                  |  |  |

| B,D,G,H,I, N/PAL                     | AM                   | 4.43361875                    |  |  |

| Combination N/PAL                    | AM                   | 3.58206525                    |  |  |

| SECAM                                | FM                   | 4.40625 or 4.25               |  |  |

| Con a con Ma  | TABLE I      |              |  |

|---------------|--------------|--------------|--|

| SUMMARY OF WO | ORLDWIDE COL | OR IV SYSTEM |  |

|               |              | <b>G</b> 1   |  |

## II. PROCESSING ALGORITHM

The NTSC and PAL use Amplitude Modulation (AM) and the SECAM uses Frequency Modulation (FM) to transmit color component signals. Therefore, data processing of NTSC and PAL differ from that of SECAM.

#### A. NTSC and PAL

To modulate the component signals based on the output formats as shown in Table 1, the YCbCr is transformed into the YUV color components by using the following transformational matrix. Eq. (1) is for both M & 4.43 modes of NTSC and M & N modes of PAL. The color space transformation such as Eq. (1) is used to prevent saturation of a modulated signal.

$$Y = 0.591 \times (Y_{601} - 16),$$

$$U = 0.504 \times (Cb - 128),$$

$$V = 0.711 \times (Cr - 128).$$

(1)

Low-pass filtering of YUV must be done to follow the channel bandwidths restricted by the standard and to increase the signals-to-noise ratio. The *Y* contains the brightness information with a 6 MHz bandwidth and the UV signals include the hue and saturation information with a bandwidth of 1.5 MHz or less [2]. A blanking pedestal is added to the filtered *Y* during active video, and the sync information is added to the partial blanking areas. In Eq. (2),  $Y_{sync}$  means the

luminance signal that is added to the pedestal, blanking and sync signal. During active video, the UV data is modulated with sine and cosine sub-carriers, it makes a chrominance(C) signal as a result. The chrominance signal is presented by:

$$C = U \sin \omega t + V \cos \omega t \text{ for NTSC}$$

=  $U \sin \omega t \pm V \cos \omega t \text{ for PAL}$  (2)

$(\omega = 2\pi f_{sc})$

Where  $f_{sc}$  is a sub-carrier frequency in Table 1. The chrominance signal for PAL has the sign of *V* alternating from one line to the next. Once the chrominance signal (*C*) is generated, CVBS is obtained easily by using *Y* and *C* like shown in Eq. (3).

$$CVBS = Y_{sync} + C \tag{3}$$

## B. Modified SECAM for Digital System

The horizontal and vertical timing for SECAM is the same things as PAL. The main difference is that SECAM uses FM modulation to convey color information whereas NTSC and PAL use AM modulation. The input YCbCr signals are transformed into YDbDr signals that represent the luminance signal of Y and two color-component signals of Db and Drbecause SECAM uses the YDbDr color space.

$$Y = 0.625 \times (Y_{601} - 16),$$

$$Db = 0.0119 \times (Cb - 128),$$

$$Dr = -0.0119 \times (Cr - 128).$$

(4)

The component signals are then pre-emphasized to generate  $Db^*$  and  $Dr^*$ . The frequency deviations are obtained by multiplying  $\Delta f_{OB}$  and  $\Delta f_{OR}$  by the integrals of the preemphasized values, respectively. The deviations are then added to the center frequencies of  $f_{OB}$  and  $f_{OR}$  to generate the FM subcarriers of sinusoidal functions. By doing so, the SECAM system can use frequency modulations to transmit the Db to one video line and the Dr to another line.

$$CVBS = Y_{sync} + G\sin 2\pi \left\{ f_{OB} + \Delta f_{OB} \int_0^t Db^*(\tau) d\tau \right\} \text{ for } Db \text{ line} \quad (5)$$

$$G\sin 2\pi \left\{ f_{OR} + \Delta f_{OR} \int_0^t Dr^*(\tau) d\tau \right\} \text{ for } Dr \text{ line} \quad (6)$$

Where  $f_{OB} = 4.25$ MHz,  $\Delta f_{OB} = 230$ kHz,  $f_{OR} = 4.40625$ MHz, and  $\Delta f_{OR} = 280$ kHz. The *G* is used to reduce the visibility of the sub-carriers in areas of low luminance and to improve the signal-to-noise ratio of highly saturated colors.

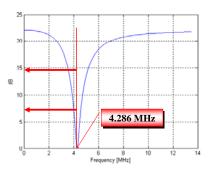

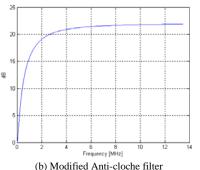

Fig. 1(a) shows the characteristic of the anti-cloche filter proposed by ITU-R standard. As we can see, the characteristic of the filter is very narrow and sharp around the  $f_0$  frequency

of 4.286MHz. It requires the filter order that needs at least one hundred coefficients for finite impulse response (FIR) filter. Thus, it is very difficult to design the anti-cloche filter in hardware. Nevertheless, it is symmetric around this frequency, fortunately. We now shift the symmetric axis to the OHz frequency as shown in Fig. 1(b). Thus, the anti-cloche filter looks like a high pass filter (HPF). However, it requires numerous filter orders because it has the gain more than 20dB within 3MHz bandwidth if it is designed by FIR filter. So we designed it with infinite impulse response (IIR) filter. This makes the hardware implementation easier. The previous FM formula in Eq. (5) and Eq. (6) must be changed to use the modified anti-cloche filter. Eq. (5) and Eq. (6) can be easily changed into Eq. (7) and Eq. (8) by using the shifting factors of  $f_{O}t$  and  $-f_{O}t$  in order to derive the HPF of the modified anticloche filter. The  $f_0$  is 4.286MHz that is an axis of symmetry in the anti-cloche filter in Fig 1(a).

Although the modulation method using Eq. (7) and Eq. (8) is more complicated than it of Eq. (5) and Eq. (6), the modified anti-cloche filter in Fig. 1(b) is easy-to-design and simple when implemented to the hardware [3].

Fig. 1 Frequency response of anti-cloche filter and modified Anti-Cloche filter

$$CVBS = Y + G \sin 2\pi \left\{ f_{OB}t + \Delta f_{OB} \int_{0}^{t} Db^{*}(\tau) d\tau \right\}$$

= Y + G \sin 2\pi \left\{ f\_{O}t + (f\_{OB}t - f\_{O}t + \Delta f\_{OB} \int\_{0}^{t} Db^{\*}(\tau) d\tau) \right\}

= Y + G[\cos 2\pi f\_{O}t \cdot \sin 2\pi \left\{ (f\_{OB} - f\_{O})t + \Delta f\_{OB} \int\_{0}^{t} Db^{\*}(\tau) d\tau \right\}

+ \sin 2\pi f\_{O}t \cdot \cos 2\pi \left\{ (f\_{OB} - f\_{O})t + \Delta f\_{OB} \int\_{0}^{t} Db^{\*}(\tau) d\tau \right\} \right\}

$$(7)$$

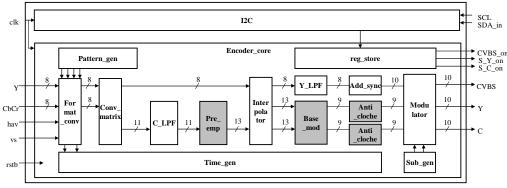

Fig. 2 Block diagram of the TV-OUT video processor

$$CVBS = Y + G \sin 2\pi \left\{ f_{OR}t + \Delta f_{OR} \int_{0}^{t} Dr^{*}(\tau) d\tau \right\}$$

=  $Y + G \sin 2\pi \left\{ f_{O}t + (f_{OR}t - f_{O}t + \Delta f_{OR} \int_{0}^{t} Dr^{*}(\tau) d\tau) \right\}$

=  $Y + G [\cos 2\pi f_{O}t \cdot \sin 2\pi \{ (f_{OR} - f_{O})t + \Delta f_{OR} \int_{0}^{t} Dr^{*}(\tau) d\tau \}$

+  $\sin 2\pi f_{O}t \cdot \cos 2\pi \{ (f_{OR} - f_{O})t + \Delta f_{OR} \int_{0}^{t} Dr^{*}(\tau) d\tau \} ]$  (8)

# III. ARCHITECTURE DESIGN

When designing any hardware system, we contemplate such issues as fabrication costs, hardware complexity, accuracy of the system, speed of operation. The proposed video processor considered the efficiency of system, primarily. Fig. 2 shows the block diagram of the proposed video processor. The processor is comprised of fourteen major building blocks. In the block diagram, the blocks that have grey color use only in the case of SECAM output mode. Thus, in the case of NTSC and PAL mode, data is bypassed through these blocks. Other blocks are used commonly for all output modes. The numerals represent the signal's bit width of each block.

Block 'Time\_gen' generates various timing signals for each block. The 'Pattern\_gen' generates two kinds of internal patterns of color bars in order to self-test the functions of the proposed TV-out video processor. The 'Format\_conv' converts the BT.656 data into BT.601 data. The 'Interpolator' up-samples the 13.5 MHz rate to the 27 MHz. The 'Conv\_matrix' converts the YCbCr into the YUV or YDbDr as shown in Eq. (1) and Eq.(4). The 'Y\_1pf' conducts digital filtering for the luminance(Y) signals as shown in Eq. (3). The 'C\_1pf' conducts digital filtering for the color component(C) signals. The block, 'Pre\_emp' is pre-emphasizing band-limited color component signals of SECAM to prevent FM signal distortion. The block, 'Anti-cloche', is filtering out and functions as the Fig. 1(b). The block, 'Base\_mod', works the low base-band modulation as Eq. (7) and Eq.(8).

The band-limited signals through the 'Y\_lpf' are then added to horizontal sync, vertical sync and blanking signals in the 'Add\_sync'. The 'Sub\_gen' generates the various sub-carriers based on output formats. The 'Modulator' modulates the bandlimited color-component signals to the sub-carriers and produces both the CVBS and the S-video of Y and C as shown in Eq. (2), Eq.(7) and Eq.(8). The programmable values in this proposed video processor are controlled through the I2C protocol. The controlled values are stored in the 'reg\_store' for the hardware operation. After the verifications are conducted, the models are synthesized into gates to see the hardware complexity by using the Synopsys synthesizer with the Samsung 0.35-um library. Total gate counts are 66,854 gates that a 2-input NAND is counted as one gate.

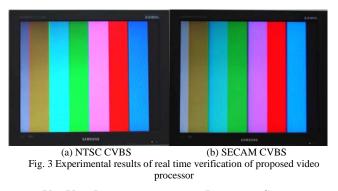

# IV. EXPERIMENTAL RESULTS

The proposed video processing system that is described by Verilog hardware description language and the designed models are verified by using the Cadence simulator [4]. The Altera FPGA APEX20KE EP20K600EBC652-3 device and 17" TFT LCD are used to demonstrate the performance of the proposed TV-out video processor [5]. Also, we verified feasibility of the proposed system.4

Fig. 3 shows experimental results of proposed video processor. Fig. 3(a) shows the display for full-screen 75% M/NTSC color Bars and Fig. 3(b) shows the display for full-screen 75% SECAM color Bars, respectively.

#### V. VLSI IMPLEMENTATION OF PROPOSED SYSTEM

The proposed system-characteristics are shown in Table 2. In addition, to compare with the implemented results of other TV-out video processors, [6] and [7] are listed in Table 2.

Chip layout of the proposed processor is shown in Fig. 4, which is implemented in Samsung 0.35um, 1-poly, 4-metal CMOS logic fabrication line with 67K logic gates(2-input

|                           | Proposed in this paper    | [6] Proposed by Joohyun | [7] Propose by<br>Analog device |

|---------------------------|---------------------------|-------------------------|---------------------------------|

| Technology                | Samsung 0.35um CMOS       | Hynix 0.35um CMOS       | Unknown                         |

| Logic gates(2-input NAND) | 67K                       | 104K                    | Unknown                         |

| Core area/mm <sup>2</sup> | 2.2 	imes 2.2 mm²         | 3.1 	imes 3.1 mm²       | Unknown                         |

| On-chip memory            | None                      | None                    | None                            |

| Supported ITU-R Standard  | NTSC,PAL ,SECAM           | NTSC,PAL, SECAM         | NTSC,PAL                        |

| Supported Input Format    | BT.601/656 YCbCr [9],[10] | BT.601/656 YCbCr        | BT.601/656 YCbCr                |

| In / Out bit width        | 8 bits /10 bits           | 10bits /10bits          | 8bits/ 10bits                   |

| Operating Frequency       | 27MHz                     | 27MHz                   | 27MHz                           |

| Core Supply Voltage       | 3.3V only                 | 3.3V / 5V               | 5V only                         |

Table II

Comparison With Some TV-out Video Processors

NAND gate) in 2.2mm x 2.2 mm die. It is captured by Synopsys Astro layout tool. We tested the proposed chip by using the logic analyzer of Agilent 1684A. Fig. 5 shows the result of test, which means that the chip is normally activated. In the power consumption, the power will be constantly consumed if all blocks are supplied with clock. So, we designed the system so as to cut off the clock supply to the anti-cloche filter and base-modulation blocks in case of NTSC or PAL. In brief, the anti-cloche filter and base-modulation for SECAM are not activated when output mode is NTSC or PAL. Consequently, the proposed system can actively control the power consumption by output mode [8].

Digital Logic

Fig. 4 The chip layout of proposed system that captured in ASTRO tool

| Scale 2 us/div 🗄 💷 🖬 Delay 56.662566 us 🔋 🔀 💷 💌 |                |                                            |  |

|-------------------------------------------------|----------------|--------------------------------------------|--|

|                                                 |                | €MI                                        |  |

| Bus/Signal                                      | Simple Trigger | 50.7 us 52.7 us 54.7 us 56.7 us 58.7 us 66 |  |

| Sample Nurr                                     |                | 1324                                       |  |

| ⊞–∰ CVBS                                        | =. 🖇 🔳         | 282 240 16                                 |  |

| Time                                            |                | 49.04 us                                   |  |

| Time                                            |                |                                            |  |

Fig. 5 Test of chip using logic analyzer

## VI. CONCLUSIONS

This paper presented the VLSI implementation of the efficient TV-OUT video processor that supports all worldwide standards such as NTSC, PAL and SECAM. By using the modified anti-cloche filter in SECAM, the hardware

complexity of the proposed processor is decreased since the design of the high pass filter shown in Fig. 1(b) is simpler than that of the very narrow band rejection filter shown in Fig. 1(a). Moreover, we can obtain the simplified structure of the video processor because NTSC, PAL and SECAM have the common data path. The display of composite video signals on the TV screen was also experimentally tested to demonstrate the feasibility of the proposed video processor. It was fabricated in the Samsung 0.35um 1-poly, 4-metal CMOS technology. The proposed TV-out video processor can be reused throughout the world for various consumer products such as mobile camera phones, laptop computers, PMPs, etc.

#### ACKNOWLEDGMENT

This work has been supported in part by the  $2^{nd}$  BK21 funded by the Korean Government. The authors also wish to thank the IDEC for its software assistance.

#### REFERENCES

- [1] Conventional Television Systems, ITU-R BT.470-6, 1998.

- [2] K. Jack, Video Demystfied: a Handbook for the Digital Engineer, 2nd e d., LLH Technology Pubilishing, Eagle Rock, 2001.

- [3] S. Lee, W. Jang, J. Ha, J. Kim, and B. Kang, "Implementation of compact TV-out video processor for portable digital device" *The Korea Institute of Signal Processing and Systems*, Vol. 7- 4, pp. 207-213, Nov. 2006.

- [4] S. Palnitkar, Verilog HDL A guide to Digital Design and synthesis, Prentice Hall, 2001.

- [5] "FPGA Device APEX20K600EBC652-3 data sheet," Altera Corporation, San Jose, U.S.A.

- [6] J. Kim, S. Lee, W. Jang, and B. Kang, "Implementation of Multistandard Video Processor for TV-OUT," *International System On Chip Conference*, 2006, p689-670.

- [7] "Digital PAL/NTSC Video Encoder with 10-Bit SSAFTM and Advanced Power Management ADV7170/ADV7171 data sheet," Analog Device, Norwood, U.S.A.

- [8] S. Lee, "Implementation of simplified TV-out Video Processor Preservin g image quality," M. Eng. Thesis, Dong-A University, Busan, South Korea, Feb. 2006.

- [9] Studio Encoding Parameters of Digital Television For Standard 4:3 and Wide-screen 16.9 Aspect Ratios, ITU-R BT 601-5, 1995.

- [10] Interfaces for digital component video signals in 525-line and 625 line television systems operating at the 4:2:2 level of recommendation ITU-R BT 601, ITU-R BT.656-4, 1998.