# Formal Certification of Android Bytecode

Alwen Tiu School of Computer Engineering Nanyang Technological University Email: atiu@ntu.edu.sg Hendra Gunadi Research School of Computer Science The Australian National University Email: hendra.gunadi@anu.edu.au Rajeev Gore Research School of Computer Science The Australian National University Email: rajeev.gore@anu.edu.au

Abstract—Android is an operating system that has been used in a majority of mobile devices. Each application in Android runs in an instance of the Dalvik virtual machine, which is a register-based virtual machine (VM). Most applications for Android are developed using Java, compiled to Java bytecode and then translated to DEX bytecode using the dx tool in the Android SDK. In this work, we aim to develop a typebased method for certifying non-interference properties of DEX bytecode, following a methodology that has been developed for Java bytecode certification by Barthe et al. To this end, we develop a formal operational semantics of the Dalvik VM, a type system for DEX bytecode, and prove the soundness of the type system with respect to a notion of non-interference. We then study the translation process from Java bytecode to DEX bytecode, as implemented in the dx tool in the Android SDK. We show that an abstracted version of the translation from Java bytecode to DEX bytecode preserves the non-interference property. More precisely, we show that if the Java bytecode is typable in Barthe et al's type system (which guarantees non-interference) then its translation is typable in our type system. This result opens up the possibility to leverage existing bytecode verifiers for Java to certify non-interference properties of Android bytecode.

#### I. INTRODUCTION

Android is an operating system that has been used in many mobile devices. According to [1], Android has the largest market share for mobile devices, making it an attractive target for malwares, so verification of the security properties of Android apps is crucial. To install an application, users can download applications from Google Play or third-party app stores in the form of an Android Application Package (APK). Each of these applications runs in an instance of a Dalvik virtual machine (VM) on top of the Linux operating system. Contained in each of these APKs is a DEX file containing specific instructions [2] to be executed by the Dalvik VM, so from here on we will refer to these bytecode instructions as DEX instructions. The Dalvik VM is a register-based VM, unlike the Java Virtual Machine (JVM) which is a stack-based VM. Dalvik is now superseded by a new runtime framework called ART, but this does not affect our analysis since both Dalvik and ART use the same DEX instructions.

We aim at providing a framework for constructing trust-worthy apps, where developers of apps can provide guarantees that the (sensitive) information the apps use is not leaked outside the device without the user's consent. The framework should also provide a mean for the end user to verify that apps constructed using the framework adhere to their advertised security policies. This is, of course, not a new concept, and it is essentially a rehash of the (foundational) proof carrying code (PCC) [3], [4], applied to the Android setting. We follow a

type-based approach for restricting information flow [5] in Android apps. Semantically, information flow properties of apps are specified via a notion of non-interference [6]. In this setting, typeable programs are guaranteed to be non-interferrent, with respect to a given policy, and typing derivations serve as certificates of non-interference. Our eventual goal is to produce a compiler tool chain that can help developers to develop Android applications that complies with a given policy, and automate the process of generating the final non-interference certificates for DEX bytecode.

An Android application is typically written in Java and compiled to Java classes (JVM bytecode). Then using tools provided in the Android Software Development Kit (SDK), these Java classes are further compiled into an Android application in the form of an APK. One important tool in this compilation chain is the dx tool, which will aggregate the Java classes and produce a DEX file to be bundled together with other resource files in the APK. Non-interference type systems exist for Java source code [7], JVM [8] and (abstracted) DEX bytecode without exception handling mechanism [9]. To build a framework that allows end-to-end certificate production, one needs to study certificate translation between these different type systems. The connection between Java and JVM type systems for non-interference has been studied in [10]. In this work, we fill the gap by showing that the connection between JVM and DEX type systems. Our contributions are the following:

- We give a formal account of the compilation process from JVM bytecode to DEX bytecode as implemented in the official dx tool in Android SDK. Section VI details some of the translation processes.

- We provide a proof that the translation from JVM to DEX preserves typeability. That is, JVM programs typeable in the non-interference type system for JVM translates into typeable programs in the noninterference type system for DEX.

The development of the operational semantics and the type systems for DEX bytecode follows closely the framework set up in [8]. Although Dalvik is a registered-based machine and JVM is a stack-based machine, the translation from one instruction set to the other is for most part quite straightforward. The adaptation of the type system for JVM to its DEX counterpart is complicated slightly by the need to simulate JVM stacks in DEX registered-based instructions. The non-trivial parts are when we want to capture both direct (via operand stacks) and indirect information flow (e.g., those resulting from branching on high value). In [8], to deal with

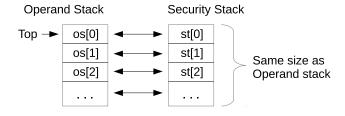

both direct and indirect flow, several techniques are used, among others, the introduction of operand stack types (each stack element carries a type which is a security label), a notion of safe control dependence region (CDR), which keeps track of the regions of the bytecode executing under a 'high' security level, and the notion of security environment, which attaches security levels to points in programs. Since Dalvik is a registerbased machine, when translating from JVM to DEX, the dx tool simulates the operand stack using DEX registers. As the type system for JVM is parameterised by a safe CDR and a security environment, we also need to define how these are affected by the translation, e.g., whether one can construct a safe CDR for DEX given a safe CDR for JVM. This was complicated by the fact that the translation by dx in general is organized along blocks of sequential (non-branching) codes, so one needs to relate blocks of codes in the image of the translation back to the original codes (see Section VI).

The rest of the paper is organized as follows: in the next section we describe some work done for Java bytecode security and the work on static analysis for Android bytecode. This is important as what we are doing is bridging the relationship between these two security measures. Then we review the work of Barthe et.al. on a non-interferent type system for JVM bytecode. In the remainder of the paper we will describe our work, namely providing the type system for DEX and proving the translation of typability. We also give examples to demonstrate how our methodology is able to detect interference by failure of typability. Before concluding, we provide our design of implementation for the proof of concept.

#### II. RELATED WORK

As we already mentioned, our work is heavily influenced by the work of Barthe et. al. [11], [8] on enforcing noninterference via type systems. We discuss other related work in the following.

The cloest to our work is the Cassandra project [9], [12], that aims at developing certified app stores, where apps can be certified, using an information-flow type system similar to ours, for absence of specific information flow. Specifically, the authors of [9], [12] have developed an abstract Dalvik language (ADL), similar to Dalvik bytecode, and a type system for enforcing non-interference properties for ADL. Our type system for Dalvik has many similarities with that of Cassandra, but one main difference is that we consider a larger fragment of Dalvik, which includes exception handling, something that is not present in Cassandra. We choose to deal directly with Dalvik rather than ADL since we aim to eventually integrate our certificate compilation into existing compiler tool chains for Android apps, without having to modify those tool chains.

Bian et. al. [13] targets the JVM bytecode to check whether a program has the non-interference property. Differently from Barthe et. al. their approach uses the idea of the compilation technique where they analyse a variable in the bytecode for its definition and usage. Using this dependence analysis, their tool can detect whether a program leaks confidential information. This is an interesting technique in itself and it is possible to adopt their approach to analyze DEX bytecode. Nevertheless, we are more interested in the transferability of properties instead of the technique in itself, i.e., if we were to use their

approach instead of a type system, the question we are trying to answer would become "if the JVM bytecode is non-interferent according to their approach, is the compiled DEX bytecode also non-interferent?".

In the case of preservation of properties itself the idea that a non-optimizing compiler preserves a property is not something new. The work by Barthe et. al. [11] shows that with a non-optimizing compiler, the proof obligation from a source language to a simple stack based language will be the same, thus allowing the reuse of the proof for the proof obligation in the source language. In showing the preservation of a property, they introduce the source imperative language and target language for a stack-based abstract machine. This is the main difference with our work where we are analyzing the actual dx tool from Android which compiles the bytecode language for stack-based virtual machine (JVM bytecode) to the actual language for register-based machine (DEX bytecode). There are also works that address this non-interference preservation from Java source code to JVM bytecode [10]. Our work can then be seen as a complement to their work in that we are extending the type preservation to include the compilation from JVM bytecode to DEX bytecode.

To deal with information flow properties in Android, there are several works addressing the problem [14], [15], [16], [17], [18], [19], [20], [21], [22], [23] although some of them are geared towards the privilege escalation problem. These works base their context of Android security studied in [23]. The tool in the study, which is called Kirin, is also of great interest for us since they deal with the certification of Android applications. Kirin is a lightweight tool which certifies an Android application at install time based on permissions requested. Some of these works are similar to ours in a sense working on static analysis for Android. The closest one to mention is ScanDroid [14], with the underlying type system and static analysis tool for security specification in Android [24]. Then along the line of type system there is also work by Bugliesi et. al. called Lintent that tries to address noninterference on the source code level [15]. The main difference with what we do lies in that the analysis itself is relying on the existence of the source (the JVM bytecode for ScanDroid and Java source code for Lintent) from which the DEX program is translated.

There are some other static analysis tools for Android which do not stem from the idea of type system, e.g. Trust-Droid [17] and ScanDal [18]. TrustDroid is another static analysis tool on Android bytecode, trying to prevent information leaking. TrustDroid is more interested in doing taint analysis on the program, although different from TaintDroid [16] in that TrustDroid is doing taint analysis statically from decompiled DEX bytecode whereas TaintDroid is enforcing run time taint analysis. ScanDal is also a static analysis for Android applications targetting the DEX instructions directly, aggregating the instructions in a language they call Dalvik Core. They enumerate all possible states and note when any value from any predefined information source is flowing through a predefined information sink. Their work assumed that predefined sources and sinks are given, whereas we are more interested in a flexible policy to define them.

Since the property that we are interested in is non-interference, it is also worth mentioning Sorbet, a run time

```

binop op

binary operation on stack

\operatorname{push} c

push value on top of a stack

pop value from top of a stack

pop

swap top two operand stack values

swap

load x

load value of x on stack

store x

store top of stack in variable x

conditional jump

ifeq j

goto j

unconditional jump

return the top value of the stack

return

\mathbf{new}\ C

create new object in the heap

load value of field fon stack

getfield f

putfield f

store top of stack in field f

newarray t

create new array of type t in the heap

arraylength

get the length of an array

arrayload

load value from an array

arraystore

store value in array

invoke m_{\rm ID}

Invoke method indicated by m_{\rm ID}

with arguments on top of the stack

throw

Throw exception at the top of a stack

where op \in \{+, -, \times, /\}, c \in \mathbb{Z}, x \in \mathcal{X}, j \in \mathcal{PP}, C \in \mathcal{C},

f \in \mathcal{F}, t \in \mathcal{T}_J, and m_{\mathrm{ID}} \in \mathcal{M}.

```

Fig. 1: JVM Instruction List

enforcement of the property by modifying the Android operating system [19], [20]. Their approach is different from our ultimate goal which motivates this work in that we are aiming for no modification in the Android operating system.

## III. Type System for JVM

In this section, we give an overview of Barthe et. al's type system for JVM. Due to space constraints, some details are omitted and the reader is referred to [8] for a more detailed explanation and intuitions behind the design of the type system. Readers who are already familiar with the work of Barthe et. al may skip this section.

A program P is given by its list of instructions given in Figure 1. The set  $\mathcal{X}$  is the set of local variables,  $\mathcal{V} = \mathbb{Z} \cup \mathcal{L} \cup \{null\}$  is the set of values, where  $\mathcal{L}$  is an (infinite) set of locations and null denotes the null pointer, and  $\mathcal{PP}$  is the set of program points. We use the notation \* to mean that for any set X,  $X^*$  is a stack of elements of X. Programs are also implicitly parameterized by a set  $\mathcal{C}$  of class names, a set  $\mathcal{F}$  of field identifiers, a set  $\mathcal{M}$  of method names, and a set of Java types  $\mathcal{T}_J$ . The instructions listing can be seen in Figure 1.

Operational Semantics The operational semantics is given as a relation  $\leadsto_{m,\tau} \subseteq \operatorname{State} \times (\operatorname{State} + (\mathcal{V}, \mathbf{heap}))$  where m indicates the method under which the relation is considered and  $\tau$  indicates whether the instruction is executing normally (indicated by Norm) or throwing an exception. (sometimes we omit m whenever it is clear which m we are referring to, we may also remove  $\tau$  when it is clear from the context whether the instruction is executing normally or not ). State here represents a set of JVM states, which is a tuple  $\langle i, \rho, os, h \rangle$  where  $i \in \mathcal{PP}$  is the program counter that points to the next

instruction to be executed;  $\rho \in \mathcal{X} \to \mathcal{V}$  is a partial function from local variables to values,  $os \in \mathcal{V}^*$  is an operand stack, and  $h \in \mathbf{heap}$  is the heap for that particular state. Heaps are modeled as partial functions  $\mathbf{h} : \mathcal{L} \to \mathcal{O} + \mathcal{A}$ , where the set  $\mathcal{O}$  of objects is modeled as  $\mathcal{C} \times (\mathcal{F} \to \mathcal{V})$ , i.e. each object  $o \in \mathcal{O}$  possess a class class(o) and a partial function to access field values, which is denoted by o.f to access the value of field f of object  $o.\mathcal{A}$  is the set of arrays modeled as  $\mathbb{N} \times (\mathbb{N} \to \mathcal{V}) \times \mathcal{PP}$  i.e. each array has a length, partial function from index to value, and a creation point. The creation point will be used to define the notion of array indistinguishability. Heap is the set of heaps.

The program also comes equipped with a partial function  $\mathbf{Handler_m}: \mathcal{PP} \times \mathcal{C} \to \mathcal{PP}$ . We write  $\mathbf{Handler_m}(i,C) = t$  for an exception of class  $C \in \mathcal{C}$  thrown at program point i, which will be caught by a handler with its starting program point t. In the case where the exception is uncaught, we write  $\mathbf{Handler_m}(i,C) \uparrow$  instead. The final states will be  $(\mathcal{V} + \mathcal{L}) \times \mathbf{Heap}$  to differentiate between normal termination  $(v,h) \in \mathcal{V} \times \mathbf{Heap}$ , and an uncaught exception  $(\langle l \rangle, h) \in \mathcal{L} + \mathbf{Heap}$  which contains the location l for the exception in the heap h.

op denotes here the standard interpretation of arithmetic operation of op in the domain of values  $\mathcal{V}$  (although there is no arithmetic operation on locations).

The instruction that may throw an exception primarily are method invocation and the object/array manipulation instructions.  $\{np\}$  is used as the class for null pointer exceptions, with the associated exception handler being **RuntimeExceptionHandling**. The transitions are also parameterized by a tag  $\tau \in \{Norm\} + \mathcal{C}$  to describe whether the transition occurs normally or some exception is thrown.

Some last remarks: firstly, because of method invocation, the operational semantics will also be mixed with a big step semantics style  $\rightsquigarrow_m^+$  from method invocations of method m and its associated result, to be more precise  $\rightsquigarrow_m^+$  is a transitive closure of  $\rightsquigarrow_m$ . Then, for instructions that may not throw an exception, we remove the subscript  $\{m, \text{Norm}\}$  from  $\rightsquigarrow$  because it is clear that they have no exception throwing operational semantic counterpart. A list of operational semantics are contained in Figure 2. We do not show the full list of operational semantics due to space limitations. However, the interested reader can see Figure 7 in Appendix C for the full list of JVM operational semantics.

**Successor Relation** The successor relation  $\mapsto \subseteq \mathcal{PP} \times \mathcal{PP}$  of a program P are tagged with whether the execution is normal or throwing an exception. According to the types of instructions at program point i, there are several possibilities:

- $P_m[i] = \mathbf{goto}\ t$ . The successor relation is  $i \mapsto^{\text{Norm}} t$

- $P_m[i]$  = ifeq t. In this case, there are 2 successor relations denoted by  $i \mapsto^{\text{Norm}} i + 1$  and  $i \mapsto^{\text{Norm}} t$ .

- $P_m[i] = \mathbf{return}$ . In this case it is a return point denoted by  $i \mapsto^{\text{Norm}}$

- P<sub>m</sub>[i] is an instruction throwing a null pointer exception, and there is a handler for it (Handler(i, np) = t). In this case, the successor is t denoted by i → np t.

$$\frac{P_m[i] = \mathbf{push} \ n}{\langle i, \rho, os \rangle \rightsquigarrow \langle i+1, \rho, n :: os \rangle} \quad \frac{P_m[i] = \mathbf{pop}}{\langle i, \rho, v :: os \rangle \rightsquigarrow \langle i+1, \rho, os \rangle} \quad \frac{P_m[i] = \mathbf{return}}{\langle i, \rho, v :: os \rangle \rightsquigarrow v, h} \quad \frac{P_m[i] = \mathbf{goto} \ j}{\langle i, \rho, os \rangle \rightsquigarrow \langle j, \rho, os \rangle}$$

$$\frac{P_m[i] = \mathbf{store} \ x \ x \in \mathbf{dom}(\rho)}{\langle i, \rho, v :: os \rangle \rightsquigarrow \langle i+1, \rho \oplus \{x \mapsto v\}, os \rangle} \quad \frac{P_m[i] = \mathbf{load} \ x}{\langle i, \rho, os \rangle \rightsquigarrow \langle i+1, \rho, \rho(x) :: os \rangle} \quad \frac{P_m[i] = \mathbf{binop} \ op \quad n_2 \ \underline{op} \ n_1 = n}{\langle i, \rho, n_1 :: n_2 :: os \rangle \rightsquigarrow \langle i+1, \rho, n :: os \rangle}$$

$$\frac{P_m[i] = \mathbf{swap}}{\langle i, \rho, v_1 :: v_2 :: os \rangle \rightsquigarrow \langle i+1, \rho, v_2 :: v_1 :: os \rangle} \quad \frac{P_m[i] = \mathbf{ifeq} \ j \quad n \neq 0}{\langle i, \rho, n :: os \rangle \rightsquigarrow \langle i+1, \rho, os \rangle} \quad \frac{P_m[i] = \mathbf{ifeq} \ j \quad n = 0}{\langle i, \rho, n :: os \rangle \rightsquigarrow \langle j, \rho, os \rangle}$$

Fig. 2: JVM Operational Semantic (Selected)

- P<sub>m</sub>[i] is an instruction throwing a null pointer exception, and there is no handler for it (Handler(i, np) ↑

). In this case it is a return point denoted by i → np.

- $P_m[i] = \mathbf{throw}$ , throwing an exception  $C \in \mathbf{classAnalysis}(m,i)$ , and  $\mathbf{Handler}(i,C) = t$ . The successor relation is  $i \mapsto^C t$ .

- $P_m[i] = \mathbf{throw}$ , throwing an exception  $C \in \mathbf{classAnalysis}(m,i)$ , and  $\mathbf{Handler}(i,C) = t$ . It is a return point and the successor relation is  $i \mapsto^C$ .

- $P_m[i]$  = invoke  $m_{\text{ID}}$ , throwing an exception  $C \in \text{excAnalysis}(m_{\text{ID}})$ , and Handler(i, C) = t. The successor relation is  $i \mapsto^C t$ .

- $P_m[i]$  = invoke  $m_{\mathrm{ID}}$ , throwing an exception  $C \in \mathbf{excAnalysis}(m_{\mathrm{ID}})$ , and  $\mathbf{Handler}(i,C) \uparrow$ . It is a return point and the successor relation is  $i \mapsto^C$ .

- $P_m[i]$  is any other cases. The successor is its immediate instruction denoted by  $i \mapsto^{norm} i + 1$

**Typing Rules** The security level is defined as a partially ordered set  $(S, \leq)$  of security levels S that form a lattice.  $\sqcup$  denotes the lub of two security levels, and for every  $k \in S$ , lift is a point-wise extension to stack types of  $\lambda l.k \sqcup l$ . The policy of a method is also defined relative to a security level  $k_{\rm obs}$  which denotes the capability of an observer to observe values from local variables, fields, and return values whose security level are below  $k_{\rm obs}$ . The typing rules are defined in terms of stack types, that is a stack that associates a value in the operand stack to the set of security levels S. The stack type itself takes the form of a stack with corresponding indices from the operand stack, as shown below.

We assume that a method comes with its security policy of the form  $\vec{k_a} \stackrel{k_h}{\to} \vec{k_r}$  where  $\vec{k_a}$  represents a list  $\{v_1:k_1,\ldots,v_n:k_n\}$  with  $k_i \in \mathcal{S}$  being the security level of local variables

$v_i \in \mathcal{R}, \ k_h$  is the effect of the method on the heap and  $\vec{k_r}$  is the return signature, i.e. the security levels of the return value. The return signature is of the form of a list to cater for the possibility of an uncaught exception on top of the normal return value. The  $\vec{k_r}$  is a list of the form  $\{\text{Norm}: k_n, e_1: k_{e_1}, \ldots, e_n: k_{e_n}\}$  where  $k_n$  is the security level for the normal return value, and  $e_i$  is the class of the uncaught exception thrown by the method and  $k_{e_i}$  is the associated security level. In the sequel, we write  $\vec{k_r}[n]$  to stand for  $k_n$  and  $\vec{k_r}[e_i]$  to stand for  $k_{e_i}$ . An example of this policy can be  $\{1:L,2:H\} \xrightarrow{H} \{\text{Norm}:L\}$  where  $L,H \in \mathcal{S}, L \leq k_{\text{obs}}, H \nleq k_{\text{obs}}$  which indicates that the method will return a low value, and that throughout the execution of the method, the security level of local variable 1 will be low while the security level of local variable 2 will be high.

Arrays have an extended security level than that of the usual object or value to cater for the security level of the contents. The security level of an array will be of the form  $k[k_c]$  where k represents the security level of an array and  $k_c$  will represent the security level of its content (this implies that all array elements have the same security level  $k_c$ ). Denote  $\mathcal{S}^{\text{ext}}$  as the extension of security levels  $\mathcal{S}$  to define the array's security level. The partial order on  $\mathcal{S}$  will also be extended with  $\leq^{\text{ext}}$ :

$$\frac{k \le k' \quad k, k' \in \mathcal{S}}{k \le^{\text{ext}} k'} \qquad \frac{k \le k' \quad k, k' \in \mathcal{S} \quad k_c \in \mathcal{S}^{\text{ext}}}{k \lceil k_c \rceil}$$

Generally, in the case of a comparison between extended level  $k[k_c] \in \mathcal{S}^{\mathrm{ext}}$  and a standard level  $k' \in \mathcal{S}$ , we only compare k and k' w.r.t. the partial order on  $\mathcal{S}$ . In the case of comparison with  $k_{\mathrm{obs}}$ , since  $k_{\mathrm{obs}} \in \mathcal{S}$  an extended security  $k[k_c]$  is considered low (written  $k[k_c] \leq k_{\mathrm{obs}}$ ) if  $k \leq k_{\mathrm{obs}}$ . Only  $k_{\mathrm{obs}}$  and se (defined later) will stay in the form of  $\mathcal{S}$ , everything else will be extended to also include the extended level  $\mathcal{S}^{\mathrm{ext}}$ .

The transfer rules come equipped with a security policy for fields  $\mathbf{ft}: \mathcal{F} \to \mathcal{S}^{\mathrm{ext}}$  and  $\mathbf{at}: \mathcal{PP} \to \mathcal{S}^{\mathrm{ext}}$  that maps the creation point of an array with the security level of its content.  $\mathbf{at}(a)$  will also be used to denote the security level of the content of array a at its creation point.

The notation  $\Gamma$  is used to define the table of method signatures which will associate a method identifier  $m_{\rm ID}$  and a security level  $k \in \mathcal{S}$  (of the object invoked) to a security

$$\frac{P_m[i] = \mathbf{load} \ x}{se, i \vdash st \Rightarrow (\vec{k_v}(x) \sqcup se(i)) :: st} \qquad \frac{P[i]_m = \mathbf{store} \ x}{se, i \vdash k :: st \Rightarrow st} \qquad \frac{P_m[i] = \mathbf{swap}}{i \vdash k_1 :: k_2 :: st \Rightarrow k_2 :: k_1 :: st}$$

$$\frac{P[i]_m = \mathbf{ifeq} \ j \quad \forall j' \in \mathbf{region}(i, \mathrm{Norm}), k \leq se(j')}{\mathbf{region}, se, i \vdash k :: st \Rightarrow \mathbf{lift_k}(st)} \qquad \frac{P_m[i] = \mathbf{goto} \ j}{i \vdash st \Rightarrow st} \qquad \frac{P_m[i] = \mathbf{push} \ n}{i \vdash st \Rightarrow se(i) :: st}$$

$$\frac{P[i]_m = \mathbf{binop} \ op}{se, i \vdash k_1 :: k_2 :: st \Rightarrow (k_1 \sqcup k_2 \sqcup se(i)) :: st} \qquad \frac{P_m[i] = \mathbf{return} \quad se(i) \sqcup k \leq k_r[n]}{\vec{k_a} \stackrel{k_h}{\Rightarrow} \vec{k_r}, se, i \vdash k :: st \Rightarrow} \qquad \frac{P_m[i] = \mathbf{pop}}{i \vdash k :: st \Rightarrow st}$$

Fig. 3: JVM Transfer Rule (Selected)

signature  $\Gamma_{m_{\rm ID}}[k]$ . The collection of security signatures of a method m is defined as Policies<sub> $\Gamma$ </sub> $(m_{\rm ID}) = {\Gamma_{m_{\rm ID}}[k] \mid k \in \mathcal{S}}$ .

A method is also parameterized by a control dependence region (CDR) which is defined in terms of two functions: region and jun. The function region :  $\mathcal{PP} \to \wp(\mathcal{PP})$  can be seen as all the program points executing under the guard of the instruction at the specified program point, i.e. in the case of region(i) the guard will be program point i. The function  $\mathbf{jun}(i)$  itself can be seen as the nearest program point which all instructions in  $\mathbf{region}(i)$  have to execute (junction point). A CDR is safe if it satisfies the following SOAP (Safe Over APproximation) properties.

**Definition III.1.** A CDR structure (region, jun) satisfies the SOAP properties if the following properties hold:

SOAP1.  $\forall i, j, k \in \mathcal{PP}$  and  $tag \tau$  such that  $i \mapsto j$  and  $i \mapsto^{\tau} k$  and  $j \neq k$  (i is hence a branching point),  $k \in \mathbf{region}(i,\tau)$  or  $k = \mathbf{jun}(i,\tau)$ .

SOAP2.  $\forall i, j, k \in \mathcal{PP}$  and tag  $\tau$ , if  $j \in \mathbf{region}(i, \tau)$  and  $j \mapsto k$ , then either  $k \in \mathbf{region}(i, \tau)$  or  $k = \mathbf{jun}(i, \tau)$ .

SOAP3.  $\forall i, j \in \mathcal{PP}$  and tag  $\tau$ , if  $j \in \mathbf{region}(i, \tau)$  and j is a return point then  $\mathbf{jun}(i, \tau)$  is undefined.

SOAP4.  $\forall i \in \mathcal{PP}$  and tags  $\tau_1, \tau_2$  if  $\mathbf{jun}(i, \tau_1)$  and  $\mathbf{jun}(i, \tau_2)$  are defined and  $\mathbf{jun}(i, \tau_1) \neq \mathbf{jun}(i, \tau_2)$  then  $\mathbf{jun}(i, \tau_1) \in \mathbf{region}(i, \tau_2)$  or  $\mathbf{jun}(i, \tau_2) \in \mathbf{region}(i, \tau_1)$ .

SOAP5.  $\forall i, j \in \mathcal{PP}$  and tag  $\tau$ , if  $j \in \mathbf{region}(i, \tau)$  and j is a return point then for all tags  $\tau'$  such that  $\mathbf{jun}(i, \tau')$  is defined,  $\mathbf{jun}(i, \tau') \in \mathbf{region}(i, \tau)$ .

SOAP6.  $\forall i \in \mathcal{PP}$  and tag  $\tau_1$ , if  $i \mapsto^{\tau_1}$  then for all tags  $\tau_2$ , region $(i, \tau_2) \subseteq \text{region}(i, \tau_1)$  and if  $\text{jun}(i, \tau_2)$  is defined,  $\text{jun}(i, \tau_2) \in \text{region}(i, \tau_1)$ .

The security environment function  $se: \mathcal{PP} \to \mathcal{S}$  is a map from a program point to a security level. The notation  $\Rightarrow$  represents a relation between the stack type before execution and the stack type after execution of an instruction.

The typing system is formally parameterized by:

$\Gamma$ : a table of method signatures, needed to define the transfer rules for method invocation;

ft: a map from fields to their global policy level; CDR: a structure consists of (region, jun).

se: security environment

sgn: method signature of the current method

thus the complete form of a judgement parameterized by a tag  $\tau \in \{\text{Norm} + \mathcal{C}\}$  is

$$\Gamma$$

, ft, region,  $se$ ,  $sgn$ ,  $i \vdash^{\tau} S_i \Rightarrow st$

although in the case where some elements are unnecessary, we may omit some of the parameters e.g.  $i \vdash S_i \Rightarrow st$

As in the operational semantics, wherever it is clear that the instructions may not throw an exception, we remove the tag Norm to reduce clutter. The transfer rules are contained in Figure 3 (for the full list of transfer rules, see Figure 8 in Appendix C). Using these transfer rules, we can then define the notion of typability:

**Definition III.2** (Typable method). A method m is typable w.r.t. a method signature table  $\Gamma$ , a global field policy  $\mathbf{ft}$ , a policy sgn, and a CDR  $\mathbf{region_m}: \mathcal{PP} \to \wp(\mathcal{PP})$  if there exists a security environment  $se: \mathcal{PP} \to \mathcal{S}$  and a function  $S: \mathcal{PP} \to \mathcal{S}^*$  s.t.  $S_1 = \epsilon$  and for all  $i, j \in \mathcal{PP}$ , and exception tags  $e \in \{\text{Norm} + \mathcal{C}\}$ :

- (a)  $i \mapsto^e j$  implies there exists  $st \in \mathcal{S}^*$  such that  $\Gamma$ , **ft**, **region**, se, sgn,  $i \vdash^e S_i \Rightarrow st$  and  $st \sqsubseteq S_j$ ;

- (b)  $i \mapsto^e implies \Gamma$ , ft, region,  $se, sgn, i \vdash^e S_i \Rightarrow$

where  $\sqsubseteq$  denotes the point-wise partial order on type stack w.r.t. the partial order taken on security levels.

The Non-interference definition relies on the notion of indistinguishability. Loosely speaking, a method is non-interferent whenever given indistinguishable inputs, it yields indistinguishable outputs. To cater for this definition, first there are definitions of indistinguishability.

To define the notions of location, object, and array indistinguishability itself Barthe et. al. define the notion of a  $\beta$  mapping.  $\beta$  is a bijection on (a partial set of ) locations in the heap. The bijection maps low objects (objects whose references might be stored in low fields or variables) allocated in the heap of the first state to low objects allocated in the heap of the second state. The object might be indistiguishable, even if their locations are different during execution.

**Definition III.3** (Value indistinguishability). *Letting*  $v, v_1, v_2 \in \mathcal{V}$ , and given a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$ , the relation  $\sim_{\beta} \subseteq \mathcal{V} \times \mathcal{V}$  is defined by the clauses:

$$null \sim_{\beta} null \quad \frac{v \in \mathcal{N}}{v \sim_{\beta} v} \quad \frac{v_1, v_2 \in \mathcal{L} \quad \beta(v_1) = v_2}{v_1 \sim_{\beta} v_2}$$

**Definition III.4** (Local variables indistinguishability). For  $\rho, \rho' : \mathcal{X} \to \mathcal{V}$ , we have  $\rho \sim_{k_{\text{obs}}, \vec{k_a}, \beta} \rho'$  if  $\rho$  and  $\rho'$  have the same domain and  $\rho(x) \sim_{\beta} \rho'(x)$  for all  $x \in \text{dom}(\rho)$  such that  $\vec{k_a}(x) \leq k_{\text{obs}}$ .

**Definition III.5** (Object indistinguishability). Two objects  $o_1, o_2 \in \mathcal{O}$  are indistinguishable with respect to a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$  (noted by  $o_1 \sim_{k_{\mathrm{obs}},\beta} o_2$ ) if and only if  $o_1$  and  $o_2$  are objects of the same class and  $o_1.f \sim_{\beta} o_2.f$  for all fields  $f \in \mathbf{dom}(o_1)$  s.t.  $\mathbf{ft}(f) \leq k_{\mathrm{obs}}$ .

**Definition III.6** (Array indistinguishability). Two arrays  $a_1, a_2 \in \mathcal{A}$  are indistinguishable w.r.t. an attacker level  $k_{\text{obs}}$  and a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$  (noted by  $a_1 \sim_{k_{\text{obs}},\beta} o_2$ ) if and only if  $a_1$ .length =  $a_2$ .length and, moreover, if  $\operatorname{at}(a_1) \leq k_{\text{obs}}$ , then  $a_1[i] \sim_{\beta} a_2[i]$  for all i such that  $0 \leq i < a_1$ .length.

**Definition III.7** (Heap indistinguishability). Two heaps  $h_1$  and  $h_2$  are indistinguishable, written  $h_1 \sim_{k_{\text{obs}},\beta} h_2$ , with respect to an attacker level  $k_{\text{obs}}$  and a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$  iff:

- $\beta$  is a bijection between  $dom(\beta)$  and  $rng(\beta)$ ;

- $\operatorname{dom}(\beta) \subseteq \operatorname{dom}(h_1)$  and  $\operatorname{rng}(\beta) \subseteq \operatorname{dom}(h_2)$ ;

- $\forall l \in \mathbf{dom}(\beta), h_1(l) \sim_{k_{\mathrm{obs}},\beta} h_2(\beta(l))$  where  $h_1(l)$  and  $h_2(\beta(l))$  are either two objects or two arrays.

**Definition III.8** (Output indistinguishability). Given an attacker level  $k_{\text{obs}}$ , a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$ , an output level  $\vec{k_r}$ , the indistinguishability of two final states in method m is defined by the clauses:

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad \vec{k_r}[n] \leq k_{\text{obs}} \rightarrow v_1 \sim_{\beta} v_2}{(v_1, h_1) \sim_{k_{\text{obs}},\beta, \vec{k_r}} (v_2, h_2)}$$

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_1(l_1)): k) \in \vec{k_r} \quad k \leq k_{\text{obs}} \quad l_1 \sim_{\beta} l_2}{(\langle l_1 \rangle, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (\langle l_2 \rangle, h_2)}$$

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_1(l_1)): k) \in \vec{k_r} \quad k \nleq k_{\text{obs}}}{(\langle l_1 \rangle, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (v_2, h_2)}$$

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_2(l_2)): k) \in \vec{k_r} \quad k \nleq k_{\text{obs}}}{(v_1, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (\langle l_2 \rangle, h_2)}$$

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_1(l_1)) : k_1) \in \vec{k_r} \quad k_1 \nleq k_{\text{obs}}}{(\mathbf{class}(h_2(l_2)) : k_2) \in \vec{k_r} \quad k_2 \nleq k_{\text{obs}}}$$

$$\frac{(\langle l_1 \rangle, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (\langle l_2 \rangle, h_2)}{(\langle l_1 \rangle, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (\langle l_2 \rangle, h_2)}$$

where  $\rightarrow$  indicates logical implication.

At this point it is worth mentioning that whenever it is clear from the usage, we may drop some subscript from the indistinguishability relation, e.g. for two indistinguishable objects  $o_1$  and  $o_2$  w.r.t. a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$  and observer level  $k_{\mathrm{obs}}$ , instead of writing  $o_1 \sim_{k_{\mathrm{obs}},\beta} o_2$  we may

drop  $k_{\rm obs}$  and write  $o_1 \sim_{\beta} o_2$  if  $k_{\rm obs}$  is obvious. We may also drop  $k_h$  from a policy  $\vec{k_a} \stackrel{k_h}{\to} \vec{k_r}$  and write  $\vec{k_a} \to \vec{k_r}$  if  $k_h$  is irrelevant to the discussion.

**Definition III.9** (Non-interferent JVM method). A method m is non-interferent w.r.t. a policy  $\vec{k_a} \rightarrow \vec{k_r}$ , if for every attacker level  $k_{\text{obs}}$ , every partial function  $\beta \in \mathcal{L} \rightarrow \mathcal{L}$  and every  $\rho_1, \rho_2 \in \mathcal{X} \rightarrow \mathcal{V}, h_1, h_2, h'_1, h'_2 \in \textit{Heap}, r_1, r_2 \in \mathcal{V} + \mathcal{L}$  s.t.

$$\begin{array}{ll} \langle 1, \rho_1, \epsilon, h_1 \rangle \leadsto_m^+ r_1, h_1' & h_1 \leadsto_{k_{\text{obs}},\beta} h_2 \\ \langle 1, \rho_2, \epsilon, h_2 \rangle \leadsto_m^+ r_2, h_2' & \rho_1 \leadsto_{k_{\text{obs}},\vec{k_a},\beta} \rho_2 \end{array}$$

there exists a partial function  $\beta' \in \mathcal{L} \to \mathcal{L}$  s.t.  $\beta \subseteq \beta'$  and

$$(r_1, h'_1) \sim_{k_{\text{obs}}, \beta', \vec{k_a}} (r_2, h'_2)$$

Because of method invocation, there will be a notion of a side effect preorder for the notion of safety.

**Definition III.10** (Side effect preorder). Two heaps  $h_1, h_2 \in$  **Heap** are side effect preordered (written as  $h_1 \leq_k h_2$ ) with respect to a security level  $k \in \mathcal{S}$  if and only if  $\mathbf{dom}(h_1) \subseteq \mathbf{dom}(h_2)$  and  $h_1(l).f = h_2(l).f$  for all location  $l \in \mathbf{dom}(h_1)$  and all fields  $f \in \mathcal{F}$  such that  $k \nleq \mathbf{ft}(f)$ .

From which we can define a *side-effect-safe* method.

**Definition III.11** (Side effect safe). A method m is side-effectsafe with respect to a security level  $k_h$  if for all local variables  $x \in \mathbf{dom}(\rho)$ ,  $\rho \in \mathcal{X} \to \mathcal{V}$ , all heaps  $h, h' \in \mathbf{Heap}$  and value  $v \in \mathcal{V}, \langle 1, \rho, \epsilon, h \rangle \Rightarrow_m^+ v, h'$  implies  $h \leq_{k_h} h'$ .

**Definition III.12** (Safe JVM method). A method m is safe w.r.t. a policy  $\vec{k_a} \stackrel{k_h}{\rightarrow} \vec{k_r}$  if m is side-effect safe w.r.t.  $k_h$  and m is non-interferent w.r.t.  $\vec{k_a} \rightarrow \vec{k_r}$ .

**Definition III.13** (Safe JVM program). A program is safe w.r.t. a table  $\Gamma$  of method signature if every method m is safe w.r.t. all policies in  $\mathbf{Policies}_{\Gamma}(m)$ .

**Theorem III.1.** Let P be a JVM typable program w.r.t. safe CDRs ( $\mathbf{region_m}, \mathbf{jun_m}$ ) and a table  $\Gamma$  of method signatures. Then P is safe w.r.t.  $\Gamma$ .

## IV. DEX TYPE SYSTEM

A program P is given by its list of instructions in Figure 4. The set  $\mathcal{R}$  is the set of DEX virtual registers,  $\mathcal{V}$  is the set of values, and  $\mathcal{PP}$  is the set of program points. Since the DEX translation involves simulation of the JVM which uses a stack, we will also distinguish the registers:

- registers used to store the local variables,

- registers used to store parameters,

- and registers used to simulate the stack.

In practice, there is no difference between registers used to simulate the stack and those that are used to store local variables. The translation of a JVM method refers to code which assumes that the parameters are already copied to the local variables.

As in the case for JVM, we assume that the program comes equipped with the set of class names  $\mathcal{C}$  and the set of fields  $\mathcal{F}$ . The program will also be extended with array manipulation

$$\begin{split} & \underbrace{P_m[i] = \mathbf{const}(r, v) \quad r \in \mathbf{dom}(\rho)}_{\langle i, \rho, h \rangle \quad \rightsquigarrow \quad \langle i+1, \rho \oplus \{r \mapsto v\}, h \rangle} & \underbrace{P[i]_m = \mathbf{ifeq}(r, j) \quad \rho(r) = 0}_{\langle i, \rho, h \rangle \quad \rightsquigarrow \quad \langle i+1, \rho, h \rangle} & \underbrace{P_m[i] = \mathbf{ifeq}(r, t) \quad \rho(r) \neq 0}_{\langle i, \rho, h \rangle \quad \rightsquigarrow \quad \langle i+1, \rho, h \rangle} \\ & \underbrace{P[i]_m = \mathbf{return}(r_s) \quad r_s \in \mathbf{dom}(\rho)}_{\langle i, \rho, h \rangle \quad \rightsquigarrow \quad \langle i+1, \rho \oplus \{r \mapsto \rho(r_s)\}, h \rangle} & \underbrace{P_m[i] = \mathbf{goto}(t)}_{\langle i, \rho, h \rangle \quad \rightsquigarrow \quad \langle i+1, \rho, h \rangle} \\ & \underbrace{P_m[i] = \mathbf{binop}(op, r, r_a, r_b) \quad r, r_a, r_b \in \mathbf{dom}(\rho) \quad n = \rho(r_a) \quad op \quad \rho(r_b)}_{\langle i, \rho, h \rangle \quad \rightsquigarrow \quad \langle i+1, \rho \oplus \{r \mapsto n\}, h \rangle} \end{split}$$

Fig. 5: DEX Operational Semantic (Selected)

| binop op                                                                                                        | $r, r_a, r_b$   | $\rho(r) = \rho(r_a)op \ \rho(r_b).$                |

|-----------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------|

| const                                                                                                           | r, v            | $ \rho(r) = v $                                     |

| move                                                                                                            | $r, r_s$        | $ \rho(r) = \rho(r_s) $                             |

| ifeq                                                                                                            | r, t            | conditional jump if $\rho(r) = 0$                   |

| ifneq                                                                                                           | r, t            | conditional jump if $s\rho(r) \neq 0$               |

| goto                                                                                                            | t               | unconditional jump                                  |

| return                                                                                                          | $r_s$           | return the value of $\rho(r_s)$                     |

| new                                                                                                             | r, c            | $\rho(r)$ = new object of class $c$                 |

| iget                                                                                                            | $r, r_o, f$     | $\rho(r) = \rho(r_o).f$                             |

| iput                                                                                                            | $r_s, r_o, f$   | $\rho(r_o).f = \rho(r)$                             |

| newarray                                                                                                        | $r, r_l, t$     | $r = \text{new array of type } t \text{ with } r_l$ |

|                                                                                                                 |                 | number of elements                                  |

| arraylength                                                                                                     | $r, r_a$        | $\rho(r)$ = $\rho(r_a)$ .length                     |

| aput                                                                                                            | $r_s, r_a, r_i$ | $\rho(r_a)[\rho(r_i)] = \rho(r_s)$                  |

| invoke                                                                                                          | $n,m,ec{p}$     | invoke $\rho(\vec{p}[0]).m$ with $n$                |

|                                                                                                                 |                 | arguments stored in $\vec{p}$                       |

| moveresult                                                                                                      | r               | store invoke's result to $r$ . Must                 |

|                                                                                                                 |                 | be placed directly after invoke                     |

| throw                                                                                                           | r               | throw the exception in $r$                          |

| move-                                                                                                           | r               | store exception in $r$ . Have to                    |

| exception                                                                                                       |                 | be the first in the handler.                        |

|                                                                                                                 |                 |                                                     |

| where $op \in \{+, -, \times, /\}, v \in \mathbb{Z}, \{r, r_a, r_b, r_s\} \in \mathcal{R}, t \in \mathcal{PP},$ |                 |                                                     |

| $c \in \mathcal{C}, f \in \mathcal{F}$ and                                                                      |                 |                                                     |

|                                                                                                                 |                 |                                                     |

Fig. 4: DEX Instruction List

instructions, and the program will come parameterized by the set of available DEX types  $\mathcal{T}_D$  analogous to Java type  $\mathcal{T}_J$ . The DEX language also deals with method invocation. As for JVM, DEX programs will also come with a set m of method names. The method name and signatures themselves are represented explicitly in the DEX file, as such the lookup function required will be different from the JVM counterpart in that we do not need the class argument, thus in the sequel we will remove this lookup function and overload that method ID to refer to the code as well. DEX uses two special registers. We will use ret for the first one which can hold the return value of a method invocation. In the case of a moveresult, the instruction behaves like a move instruction with the special register ret as the source register. The second special register is ex which stores an exception thrown for the next instruction.

Figure 4 contains the list of DEX instructions.

**Operational Semantics** A state in DEX is just  $\langle i, \rho, h \rangle$  where the  $\rho$  here is a mapping from registers to values and h is the heap. As for the JVM in handling the method invocation, operational semantics are also extended to have a big step semantics for the method invoked. Figure 5 shows some of the operational semantics for DEX instructions. Refer to Figure 9 in Appendix D for a full list of DEX operational semantics.

The successor relation closely resembles that of the JVM, instructions will have its next instruction as the successor, except jump instructions, return instructions, and instructions that throw an exception.

**Type Systems** The transfer rules of DEX are defined in terms of registers typing  $rt: (\mathcal{R} \to \mathcal{S})$  instead of stack typing. Note that this registers typing is total w.r.t. the registers used in the method. To be more concrete, if a method only uses 16 registers then rt is a map for these 16 registers to security levels, as opposed to the whole number of 65535 registers.

The transfer rules also come equipped with a security policy for fields  $\mathbf{ft}: \mathcal{F} \to \mathcal{S}^{\mathrm{ext}}$  and  $\mathbf{at}: \mathcal{PP} \to \mathcal{S}^{\mathrm{ext}}$ . Some of the transfer rules for DEX instructions are contained in Figure 6. Full transfer rules are contained in Appendix D.

The typability of the DEX closely follows that of the JVM, except that the relation between program points is  $i \vdash RT_i \Rightarrow rt, rt \sqsubseteq RT_j$ . The definition of  $\sqsubseteq$  is also defined in terms of point-wise registers. For now we assume the existence of safe CDR with the same definition as that of the JVM side. We shall see later how we can construct a safe CDR for DEX from a safe CDR in JVM. Formal definition of typable DEX method:

**Definition IV.1** (Typable method). A method m is typable w.r.t. a method signature table  $\Gamma$ , a global field policy  $\mathbf{ft}$ , a policy sgn, and a CDR  $\mathbf{region_m}: \mathcal{PP} \to \wp(\mathcal{PP})$  if there exists a security environment  $se: \mathcal{PP} \to \mathcal{S}$  and a function  $\mathbf{RT}: \mathcal{PP} \to (\mathcal{R} \to \mathcal{S})$  s.t.  $RT_1 = \vec{k_a}$  and for all  $i, j \in \mathcal{PP}$ ,  $e \in \{\text{Norm} + \mathcal{C}\}$ :

- i →<sup>e</sup> j implies there exists rt ∈ (R → S) such that Γ,

ft, region, se, sgn, i ⊢<sup>e</sup> RT<sub>i</sub> ⇒ rt and rt ⊆ RT<sub>i</sub>;

- $i \mapsto^e implies \Gamma$ , ft, region,  $se, sgn, i \vdash^e RT_i \Rightarrow$

Following that of the JVM side, what we want to establish here is not just the typability, but also that typability means

$$\frac{P_{m}[i] = \mathbf{const}(r, v)}{i \vdash rt \Rightarrow rt \oplus \{r \mapsto se(i)\}} \qquad \frac{P_{m}[i] = \mathbf{return}(r_{s}) \quad se(i) \sqcup rt(r_{s}) \leq \vec{k_{r}}[n]}{i \vdash rt \Rightarrow}$$

$$\frac{P[i] = \mathbf{move}(r, r_{s})}{i \vdash rt \Rightarrow rt \oplus \{r \mapsto (rt(r_{s}) \sqcup se(i))\}} \qquad \frac{P_{m}[i] = \mathbf{binop}(op, r, r_{a}, r_{b})}{i \vdash rt \Rightarrow rt \oplus \{r \mapsto (rt(r_{a}) \sqcup rt(r_{b}) \sqcup se(i))\}}$$

$$\frac{P_{m}[i] = \mathbf{goto}(j)}{i \vdash rt \Rightarrow rt} \qquad \frac{P_{m}[i] = \mathbf{ifeq}(r, t) \quad \forall_{j'} \in \mathbf{region}(i, \text{Norm}), se(i) \sqcup rt(r) \leq se(j')}{i \vdash rt \Rightarrow rt}$$

Fig. 6: DEX Transfer Rule (Selected)

non-interference. As in the JVM, the notion of non-interference relies on the definition of indistinguishability, while the notion of value indistinguishability is the same as that of JVM.

**Definition IV.2** (Registers indistinguishability). For  $\rho, \rho'$ :  $(\mathcal{R} \to \mathcal{V})$  and  $rt, rt' : (\mathcal{R} \to \mathcal{S})$ , we have  $\rho \sim_{k_{\text{obs}}, rt, rt', \beta} \rho'$  iff  $\forall x \notin loc R$ ,  $rt(x) = rt'(x) = k, k \nleq k_{\text{obs}}$  or rt(x) = k, rt'(x) = k',  $k \leq k_{\text{obs}}$ ,  $k' \leq k_{\text{obs}}$ ,  $\rho(x) = \rho'(x) = v$ . where  $v \in \mathcal{V}$ , and  $k, k' \in \mathcal{S}$ .

**Definition IV.3** (Object indistinguishability). Two objects  $o_1, o_2 \in \mathcal{O}$  are indistinguishable with respect to a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$  (noted by  $o_1 \sim_{k_{\text{obs}},\beta} o_2$ ) if and only if  $o_1$  and  $o_2$  are objects of the same class and  $o_1.f \sim_{\beta} o_2.f$  for all fields  $f \in \mathbf{dom}(o_1)$  s.t.  $\mathbf{ft}(f) \leq k_{\text{obs}}$ .

**Definition IV.4** (Array indistinguishability). Two arrays  $a_1, a_2 \in \mathcal{A}$  are indistinguishable w.r.t. an attacker level  $k_{\text{obs}}$  and a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$  (noted by  $a_1 \sim_{k_{\text{obs}},\beta} o_2$ ) if and only if  $a_1.\text{length} = a_2.\text{length}$  and, moreover, if  $\operatorname{at}(a_1) \leq k_{\text{obs}}$ , then  $a_1[i] \sim_{\beta} a_2[i]$  for all i such that  $0 \leq i < a_1.\text{length}$ .

**Definition IV.5** (Heap indistinguishability). Two heaps  $h_1$  and  $h_2$  are indistinguishable with respect to an attacker level  $k_{\mathrm{obs}}$  and a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$ , written  $h_1 \sim_{k_{\mathrm{obs}},\beta} h_2$ , if and only if:

- $\beta$  is a bijection between  $dom(\beta)$  and  $rng(\beta)$ ;

- $\operatorname{dom}(\beta) \subseteq \operatorname{dom}(h_1)$  and  $\operatorname{rng}(\beta) \subseteq \operatorname{dom}(h_2)$ ;

- $\forall l \in \mathbf{dom}(\beta), h_1(l) \sim_{k_{\mathrm{obs}},\beta} h_2(\beta(l))$  where  $h_1(l)$  and  $h_2(\beta(l))$  are either two objects or two arrays.

**Definition IV.6** (Output indistinguishability). Given an attacker level  $k_{\text{obs}}$ , a partial function  $\beta \in \mathcal{L} \to \mathcal{L}$ , an output level  $\vec{k_r}$ , the indistinguishability of two final states in method m is defined by the clauses:

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad \vec{k_r}[n] \leq k_{\text{obs}} \Rightarrow v_1 \sim_{\beta} v_2}{(v_1, h_1) \sim_{k_{\text{obs}},\beta, \vec{k_r}} (v_2, h_2)}$$

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_1(l_1)): k) \in \vec{k_r} \quad k \leq k_{\text{obs}} \quad l_1 \sim_{\beta} l_2}{(\langle l_1 \rangle, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (\langle l_2 \rangle, h_2)}$$

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_1(l_1)): k) \in \vec{k_r} \quad k \nleq k_{\text{obs}}}{(\langle l_1 \rangle, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (v_2, h_2)}$$

$$\frac{h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_2(l_2)): k) \in \vec{k_r} \quad k \nleq k_{\text{obs}}}{(v_1, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (\langle l_2 \rangle, h_2)}$$

$$h_1 \sim_{k_{\text{obs}},\beta} h_2 \quad (\mathbf{class}(h_1(l_1)): k_1) \in \vec{k_r} \quad k_1 \nleq k_{\text{obs}}$$

$$(\mathbf{class}(h_2(l_2)): k_2) \in \vec{k_r} \quad k_2 \nleq k_{\text{obs}}$$

$$(\langle l_1 \rangle, h_1) \sim_{k_{\text{obs}},\beta,\vec{k_r}} (\langle l_2 \rangle, h_2)$$

where  $\rightarrow$  indicates logical implication.

**Definition IV.7** (Non-interferent DEX method). A method m is non-interferent w.r.t. a policy  $\vec{k_a} \rightarrow \vec{k_r}$ , if for every attacker level  $k_{\text{obs}}$ , every partial function  $\beta \in \mathcal{L} \rightarrow \mathcal{L}$  and every  $\rho_1, \rho_2 \in \mathcal{X} \rightarrow \mathcal{V}, h_1, h_2, h'_1, h'_2 \in \mathbf{Heap}, v_1, v_2 \in \mathcal{V} + \mathcal{L}$  s.t.

$$\begin{array}{ll} \langle 1, \rho_1, h_1 \rangle \leadsto_m^+ v_1, h_1' & h_1 \leadsto_{k_{\text{obs}},\beta} h_2 \\ \langle 1, \rho_2, h_2 \rangle \leadsto_m^+ v_2, h_2' & \rho_1 \leadsto_{k_{\text{obs}},\vec{k_a},\beta} \rho_2 \end{array}$$

there exists a partial function  $\beta' \in \mathcal{L} \to \mathcal{L}$  s.t.  $\beta \subseteq \beta'$  and

$$(v_1, h'_1) \sim_{k_{\text{obs}}, \beta', \vec{k_a}} (v_2, h'_2)$$

**Definition IV.8** (Side effect preorder). Two heaps  $h_1, h_2 \in H$  eap are side effect preordered with respect to a security level  $k \in \mathcal{S}$  (written as  $h_1 \leq_k h_2$ ) if and only if  $\operatorname{dom}(h_1) \subseteq \operatorname{dom}(h_2)$  and  $h_1(l).f = h_2(l).f$  for all location  $l \in \operatorname{dom}(h_1)$  and all fields  $f \in \mathcal{F}$  such that  $k \nleq \operatorname{ft}(f)$ .

**Definition IV.9** (Side effect safe). A method m is side-effect-safe with respect to a security level  $k_h$  if for all registers in  $\rho \in \mathcal{R} \to \mathcal{V}$ ,  $\operatorname{\mathbf{dom}}(\rho) = locR$ , for all heaps  $h, h' \in \operatorname{\mathbf{Heap}}$  and value  $v \in \mathcal{V}$ ,  $\langle 1, \rho, h \rangle \rightsquigarrow_m^+ v, h'$  implies  $h \leq_{k_h} h'$ .

**Definition IV.10** (Safe DEX method). A method m is safe w.r.t. a policy  $\vec{k_a} \stackrel{k_h}{\rightarrow} \vec{k_r}$  if m is side-effect safe w.r.t.  $k_h$  and m is non-interferent w.r.t.  $\vec{k_a} \rightarrow \vec{k_r}$ .

**Definition IV.11** (Safe DEX program). A program is safe w.r.t. a table  $\Gamma$  of method signatures if every method m is safe w.r.t. all policies in Policies $\Gamma(m)$ .

**Theorem IV.1.** Let P be a DEX typable program w.r.t. safe CDRs ( $\mathbf{region_m, jun_m}$ ) and a table  $\Gamma$  of method signatures. Then P is safe w.r.t.  $\Gamma$ .

# V. EXAMPLES

Throughout our examples we will use two security levels L and H to indicate low and high security level respectively. We start with a simple example where a high guard is used to determine the value of a low variable.

**Example V.1.** Assume that local variable 1 is H and local variable 2 is L. For now also assume that  $r_3$  is the start of the registers used to simulate the stack in the DEX instructions. Consider the following JVM bytecode and its translation.

In this case, the type system for the JVM bytecode will reject this example because there is a violation in the last store 2 constraint. The reasoning is that se(i) for  $\mathbf{push}\ 1$  will be H, thus the constraint will be  $H\sqcup H\le L$  which can not be satisfied. The same goes for the DEX instructions. Since  $r_3$  gets its value from  $r_1$  which is H, the typing rule for ifeq $(r_3,l_1)$  states that se in the last instruction will be H. Since the last  $\mathbf{move}$  instruction is targetting variables in the local variables side, the constraint applies, which states that  $H\sqcup H\le L$  which also can not be satisfied, thus this program will be rejected by the DEX type system.

The following example illustrates one of the types of the interference caused by modification of low fields of a high object aliased to a low object.

**Example V.2.** Assume that  $\vec{k_a} = \{r_1 \mapsto H, r_2 \mapsto H, r_3 \mapsto L\}$  (which means local variable 1 is high, local variable 2 is high and local variable 3 is low). Also the field f is low (ft(f) = L).

```

. . .

\mathbf{new}\ C

\mathbf{new}(r_4, C)

store 3

\mathbf{move}(r_3, r_4)

load 2

\mathbf{move}(r_4, r_2)

l_1: ifeq l_2

l_1: ifeq(r_4, l_2)

\mathbf{new}\ C

\mathbf{new}(r_4, C)

goto l_3

goto(l_3)

l_2: load 3

l_2: \mathbf{move}(r_4, r_3)

l_3: store 1

l_3: \mathbf{move}(r_1, r_4)

load 1

\mathbf{move}(r_4, r_1)

push 1

\mathbf{const}(r_5,1)

putfield f

iput(r_5, r_4, f)

```

The above JVM bytecode and its translation will be rejected by the type system for the JVM bytecode because for **putfield** f at the last line there is a constraint with the security level of the object. In this case, the **load** 1 instruction will push a reference of the object with high security level, therefore, the constraint that  $L \sqcup H \sqcup L \leq L$  can not be satisfied. The same goes for the DEX type system, it will also reject the translated program. The reasoning is that the  $\mathbf{move}(r_4, r_1)$  instruction will copy a reference to the object stored in  $r_1$  which has a high security

level, therefore  $rt(r_4) = H$ . Then, at the  $iput(r_5, r_4, f)$  we won't be able to satisfy  $L \sqcup H \sqcup L \leq L$ .

This last example shows that the type system also handles information flow through exceptions.

**Example V.3.** Assume that  $\vec{k_a} = \{r_1 \mapsto H, r_2 \mapsto L, r_3 \mapsto H\}$  and  $\vec{k_r} = \{n \mapsto L, e \mapsto H, \text{np} \mapsto H\}$ . Handler $(l_2, \text{np}) = l_h$ , and for any e, Handler $(l_2, e) \uparrow$ . The following JVM bytecode and its translation will be rejected by the typing system for the JVM bytecode.

```

load 1

\mathbf{move}(r_4, r_1)

l_1: ifeq l_2

l_1: ifeq(r_4, l_2)

\mathbf{new}\ \bar{C}

\mathbf{new}(r_4, C)

store 3

\mathbf{move}(r_3, r_4)

load 3

\mathbf{move}(r_4, r_3)

l_2: invokevirtual m l_2: invoke(1, m, r_4)

push 0

\mathbf{const}(r_4,0)

ret move(r_0, r_4)

return

return(r_0)

l_h: \mathbf{const}(r_4, r_1)

l_h: push 1

return

\mathbf{move}(r_0, r_4)

goto(ret)

```

The reason is that the typing constraint for the **invokevirtual** will be separated into several tags, and on each tag of execution we will have se as high (because the local variable 3 is high). Therefore, when the program reaches **return** 2 (line 8 and 10) the constraint is violated since we have  $\vec{k_r}[n] = L$ , thus the program is rejected. Similar reasoning holds for the DEX type system as well, in that the **invoke** will have se high because the object on which the method is invoked upon is high, therefore the typing rule will reject the program because it can not satisfy the constraint when the program is about to store the value in local variable 2 (constraint  $H \le L$  is violated, where H comes from lub with se).

#### VI. TRANSLATION PHASE

Before we continue to describe the translation processes, we find it helpful to first define a construct called the basic block. The Basic block is a construct containing a group of code that has one entry point and one exit point (not necessarily one successor/one parent), has parents list, successors list, primary succesor, and its order in the output phase. There are also some auxilliary functions:

| BMap     | is a mapping function from program pointer in       |

|----------|-----------------------------------------------------|

| -        | JVM bytecode to a DEX basic block.                  |

| SBMap    | Similar to BMap, this function takes a program      |

|          | pointer in JVM bytecode and returns whether         |

|          | that instruction is the start of a DEX basic block. |

| TSMap    | A function that maps a program pointer in JVM       |

|          | bytecode to an integer denoting the index to the    |

|          | top of the stack. Initialized with the number of    |

|          | local variables as that index is the index which    |

|          | will be used by DEX to simulate the stack.          |

| NewBlock | A function to create a new Block and associate      |

|          |                                                     |

it with the given instruction.

The DEX bytecode is simulating the IVM bytecode al-

The DEX bytecode is simulating the JVM bytecode although they have different infrastructure. DEX is register-based

whereas JVM is stack-based. To bridge this gap, DEX uses registers to simulate the stack. The way it works:

- l number of registers are used to hold local variables. (1, ..., l). We denote these registers with loc R.

- Immediately after l, there are s number of registers which are used to simulate the stack  $(l+1,\ldots,l+s)$ .

Note that although in principal stack can grow indefinitely, it is impossible to write a program that does so in Java, due to the strict stack discipline in Java. Given a program in JVM bytecode, it is possible to statically determine the height of the operand stack at each program point. This makes it possible to statically map each operand stack location to a register in DEX (cf. TSMap above and Appendix A-C); see [25] for a discussion on how this can be done.

There are several phases involved to translate JVM bytecode into DEX bytecode:

**StartBlock**: Indicates the program point at which the instruction starts a block, then creates a new block for each of these program points and associates it with a new empty block.

**TraceParentChild**: Resolves the parents successors (and primary successor) relationship between blocks. Implicit in this phase is a step creating a temporary return block used to hold successors of the block containing return instruction. At this point in time, assume there is a special label called ret to address this temporary return block.

The creation of a temporary return block depends on whether the function returns a value. If it is return void, then this block contains only the instruction return-void. Otherwise depending on the type returned (integer, wide, object, etc), the instruction is translated into the corresponding **move** and **return**. The **move** instruction moves the value from the register simulating the top of the stack to register 0. Then **return** will just return  $r_0$ .

**Translate**: Translate JVM instructions into DEX instructions.

**PickOrder**: Order blocks according to "trace analysis".

**Output:** Output the instructions in order. During this phase, **goto** will be added for each block whose next block to output is not its successor. After the compiler has output all blocks, it will then read the list of DEX instructions and fix up the targets of jump instructions. Finally, all the information about exception handlers is collected and put in the section that deals with exception handlers in the DEX file structure.

**Definition VI.1** (Translated JVM Program). The translation of a JVM program P into blocks and have their JVM instructions translated into DEX instructions is denoted by ||P||, where

||P|| = Translate(TraceParentChild(StartBlock(P))).

**Definition VI.2** (Output Translated Program). The output of the translated JVM program ||P|| in which the blocks are ordered and then output into DEX program is denoted by ||P||, where

$[||P||] = \mathbf{Output}(\mathbf{PickOrder}(||P||)).$

**Definition VI.3** (Compiled JVM Program). *The compilation of a JVM program* P *is denoted by* [P], *where*

$$\llbracket P \rrbracket = \llbracket \Vert P \Vert \rrbracket.$$

Details for each of the phase can be seen in appendix A.

VII. PROOF THAT TRANSLATION PRESERVES TYPABILITY

A. Compilation of CDR and Security Environments

Since now we will be working on blocks, we need to know how the CDRs of the JVM and that of the translated DEX are related. First we need to define the definition of the successor relation between blocks.

**Definition VII.1** (Block Successor). Suppose  $a \mapsto b$  and a and b are on different blocks. Let  $B_a$  be the block containing a and  $B_b$  be the block containing b. Then  $B_b$  will be the successor of  $B_a$  denoted by abusing the notation  $B_a \mapsto B_b$ .

Before we continue on with the properties of CDR and SOAP, we first need to define the translation of **region** and **jun** since we assume that the JVM bytecode comes equipped with **region** and **jun**.

**Definition VII.2** (Region Translation and Compilation). Given a JVM  $\mathbf{region}(i, \tau)$  and P[i] is a branching instruction, let  $i_b$  be the program point in ||i|| such that  $P_{\mathrm{DEX}}[i_b]$  is a branching instruction, then

$$\begin{split} \|\mathbf{region}(i,\tau)\| &= \mathbf{region}(i_b, \|\tau\|) = \bigcup_{j \in \mathbf{region}(i,\tau)} \|j\| \\ &\quad and \\ \|\mathbf{region}(i,\tau)\| &= \mathbf{region}(i_b, \|\tau\|) = \bigcup_{j \in \mathbf{region}(i,\tau)} \|j\| \end{split}$$

**Definition VII.3** (Region Translation and Compilation for invoke).  $\forall i.P_{DEX}[i] = \text{invoke}, i + 1 \in \text{region}(i, \text{Norm})$  (i + 1 will be the program point for moveresult).

**Definition VII.4** (Region Translation and Compilation for handler).  $\forall i, j.j \in \mathbf{region}(i,\tau)$ , let  $i_e$  be the instruction in ||P[i]|| that possibly throws, then

$$\begin{aligned} & \mathbf{handler}(i_e,\tau) \in \mathbf{region}(i_e,\tau) \ \textit{in} \ \|P\| \\ & \textit{and} \\ & \mathbf{handler}(\|i_e\|,\tau) \in \mathbf{region}(\|i_e\|,\tau) \ \textit{in} \ \|P\| \end{aligned}$$

(note that the handler will point to moveexception).

**Definition VII.5** (Region for appended goto instruction).

$$\forall b \in [P]. \quad P_{DEX}[\llbracket b.\mathbf{lastAddress} \rrbracket + 1] = \mathbf{goto} \\ \rightarrow \left( \forall .i \in \mathcal{PP}_{DEX}.b.\mathbf{lastAddress} \in \mathbf{region}(i, \tau) \right) \\ \rightarrow \left( \llbracket b.\mathbf{lastAddress} \rrbracket + 1 \right) \in \mathbf{region}(i, \tau) \right)$$

where  $\rightarrow$  indicates logical implication.

**Definition VII.6** (Junction Translation and Compilation).  $\forall i, j.j = \mathbf{jun}(i,\tau)$ , let  $i_b$  be in ||P[i]|| that branch then

$$||j||[0] = \mathbf{jun}(||i||[i_b], \tau) \text{ in } ||P||$$

and

$$|||j||[0]|| = \mathbf{jun}(||i||[i_b]||, \tau) \text{ in } ||P||.$$

**Definition VII.7** (Security Environment Translation and Compilation).  $\forall i \in \mathcal{PP}, j \in [\![i]\!].se(j) = se(i)$  in  $[\![P]\!]$  and  $\forall i \in \mathcal{PP}, j \in [\![i]\!].se([\![j]\!]) = se(i)$  in  $[\![P]\!]$ .

**Lemma VII.1** (SOAP Preservation). The SOAP properties are preserved in the translation from JVM to DEX, i.e. if the JVM

program satisfies the SOAP properties, so does the translated DEX program.

## B. Compilation Preserves Typability

There are several assumption we make for this compilation. Firstly, the JVM program will not modify its self reference for an object. Secondly, since now we are going to work in blocks, the notion of se, S, and RT will also be defined in term of this addressing. A new scheme for addressing blockAddress is defined from sets of pairs (bi, j),  $bi \in blockIndex$ , a set of all block indices (label of the first instruction in the block), where  $\forall i \in \mathcal{PP}. \exists bi, j.$  s.t.bi + j = i. We also add additional relation  $\Rightarrow^*$  to denote the reflexive and transitive closure of  $\Rightarrow$  to simplify the typing relation between blocks.

We overload  $\|.\|$  and  $\|.\|$  to also apply to stack type to denote translation from stack type into typing for registers. This translation basically just maps each element of the stack to registers at the end of registers containing the local variables (with the top of the stack with larger index, i.e. stack expanding to the right), and fill the rest with high security level. More formally, if there are n local variables denoted by  $v_1,\ldots,v_n$  and stack type with the height of m (0 denotes the top of the stack), and the method has o registers (which corresponds to the maximum depth of the stack), then  $[st] = \{r_0 \mapsto \vec{k_a}(v_1),\ldots,r_{n-1}\mapsto \vec{k_a}(v_n),r_n\mapsto st[m-1],\ldots,r_{n+m-1}\mapsto st[0],r_{n+m}\mapsto H,\ldots,r_o\mapsto H\}$ . Lastly, the function  $[\![.]\!]$  is also overloaded for addressing (bi,i) to denote abstract address in the DEX side which will actually be instantiated when producing the output DEX program from the blocks.

Due to the way stack type is translated to registers typing, we find it beneficial to introduce a simple lemma that can be proved trivially (by structural induction and definition) in regards to the  $rt_1 \subseteq rt_2$  relation. In particular this lemma will relates the registers metioned in  $rt_1$  but are not mentioned in  $rt_2$ .

**Lemma VII.2** (Registers Not in Stack Less Equal). Let the number of local variables be locN. For any two stack types  $st_1, st_2, \mathbf{length}(st_1) = n, \mathbf{length}(st_2) = m, m < n$ , any register  $x \in \{r_{locN+m+1}, \dots, r_{locN+m+n}\}$ , and register types  $rt_1 = \|st_1\|, rt_2 = \|st_2\|$  we have that  $rt_1(x) \le rt_2(x)$ .

**Definition VII.8** ( $\|$ excAnalysis $\|$  and  $\|$ excAnalysis $\|$ ).

$$\forall m \in \mathcal{M}. \| \mathbf{excAnalysis}(m) \| = \mathbf{excAnalysis}(m) \text{ in } \| P \|$$

and

$\forall m \in \mathcal{M}. \llbracket \mathbf{excAnalysis}(m) \rrbracket = \mathbf{excAnalysis}(m) \ \textit{in} \ \llbracket P \rrbracket.$

**Definition VII.9** ( $\|$ classAnalysis $\|$ ) and  $\|$ classAnalysis $\|$ ). Let e be the index of the throwing instruction from  $\|i\|$ .

$$\left( \begin{array}{c} \forall m \in \mathcal{M}, i \in \mathcal{PP}. \| \mathbf{classAnalysis}(m, \|i\|[e]) \| = \\ \mathbf{classAnalysis}(m, i) \ in \ \|P\| \end{array} \right)$$

$$and$$

$$\left( \begin{array}{c} \forall m \in \mathcal{M}, i \in \mathcal{PP}. \| \mathbf{classAnalysis}(m, \|\|i\|[e]\|) \| = \\ \mathbf{classAnalysis}(m, i) \ in \ \|P\| \end{array} \right).$$

**Definition VII.10** ( $\llbracket\Gamma\rrbracket$  and  $\llbracket\Gamma\rrbracket$ ).  $\forall m \in \mathcal{M}. \llbracket\Gamma[\llbracket m \rrbracket] \rrbracket = \Gamma[m]$  in  $\llbracket P \rrbracket$  and  $\forall m \in \mathcal{M}. \llbracket\Gamma[\llbracket m \rrbracket] \rrbracket = \Gamma[m]$  in  $\llbracket P \rrbracket$ .

**Definition VII.11.**  $\forall i \in \mathcal{PP}, RT_{\|i\|[0]} = \|S_i\|.$

The idea of the proof that compilation from JVM bytecode to DEX bytecode preserves typability is that any instruction

that does not modify the block structure can be proved using Lemma VII.3, Lemma VII.4 and Lemma VII.5 to prove the typability of register typing.

Initially we state lemmas saying that typable JVM instructions will yield typable DEX instructions. Paired with each normal execution is the lemma for the exception throwing one. These lemmas are needed to handle the additional block of **moveexception** attached for each exception handler.

**Lemma VII.3.** For any JVM program P with instruction Ins at address i and tag Norm, let the length of ||Ins|| be n. Let  $RT_{||i||[0]} = ||S_i||$ . If according to the transfer rule for P[i] = Ins there exists st s.t.  $i \vdash^{Norm} S_i \Rightarrow st$  then

$$\begin{pmatrix} \forall 0 \leq j < (n-1).\exists rt'. \|i\|[j] \vdash^{\text{Norm}} \\ RT_{\|i\|[j]} \Rightarrow rt', rt' \subseteq RT_{\|i\|[j+1]} \end{pmatrix}$$

and

$$\exists rt. \|i\|[n-1] \vdash^{\text{Norm}} RT_{\|i\|[n-1]} \Rightarrow rt, rt \subseteq \|st\|$$

according to the typing rule(s) of ||Ins||.

**Lemma VII.4.** For any JVM program P with instruction Ins at address i and tag  $\tau \neq Norm$  with exception handler at address  $i_e$ . Let the length of ||Ins|| until the instruction that throws exception  $\tau$  be denoted by n. Let  $(be,0) = ||i_e||$  be the address of the handler for that particular exception. If  $i \vdash^{\tau} S_i \Rightarrow st$  according to the transfer rule for Ins, then

$$\begin{pmatrix} \forall 0 \leq j < (n-1). \exists rt'. \|i\|[j] \vdash^{\text{Norm}} \\ RT_{\|i\|[j]} \Rightarrow rt', rt' \in RT_{\|i\|[j+1]} \end{pmatrix}$$

and

$$\exists rt. \|i\|[n-1] \vdash^{\tau} RT_{\|i\|[n-1]} \Rightarrow rt, rt \in RT_{(be,0)}$$

and

$$\exists rt. (be,0) \vdash^{\text{Norm}} RT_{(be,0)} \Rightarrow rt, rt \in \|st\|$$

according to the typing rule(s) of the first n instructions in  $\|Ins\|$  and moveexception.

**Lemma VII.5.** Let Ins be an instruction at address i,  $i \mapsto j$ , st,  $S_i$  and  $S_j$  are stack types such that  $i \vdash S_i \Rightarrow st, st \sqsubseteq S_j$ . Let n be the length of ||Ins||. Let  $RT_{||i||[0]} = ||S_i||$ , let  $RT_{||j||[0]} = ||S_j||$  and rt be registers typing obtained from the transfer rules involved in ||Ins||. Then  $rt \sqsubseteq RT_{||j||[0]}$ .

We need an additional lemma to establish that the constraints in the JVM transfer rules are satisfied after the translation. This is because the definition of typability also relies on the constraint which can affect the existence of register typing.

**Lemma VII.6.** Let Ins be an instruction at program point i,  $S_i$  its corresponding stack types, and let  $RT_{\|i\|[0]} = \|S_i\|$ . If P[i] satisfy the typing constraint for Ins with the stack type  $S_i$ , then  $\forall (bj,j) \in \|i\| . P_{DEX}[bj,j]$  will also satisfy the typing constraints for all instructions in  $\|Ins\|$  with the initial registers typing  $RT_{\|i\|[0]}$ .

Using the above lemmas, we can prove the lemma that all the resulting blocks will also be typable in DEX.

**Lemma VII.7.** Let P be a Java program such that

$$\forall i, j.i \mapsto j. \exists st.i \vdash S_i \Rightarrow st \quad and \quad st \sqsubseteq S_j$$

Then ||P|| will satisfy

1) for all blocks bi, bj s.t.  $bi \mapsto bj$ ,  $\exists rt_b$ . s.t.  $RTs_{bi} \Rightarrow^* rt_b, rt_b \subseteq RTs_{bj}$ ; and

2)

$$\forall bi, i, j \in bi. \ s.t. \ (bi, i) \mapsto (bi, j). \exists rt. \ s.t. \ (bi, i) \vdash RT_{(bi, i)} \Rightarrow rt, rt \sqsubseteq RT_{(bi, j)}$$

where

$$RTs_{bi} = ||S_i|| \qquad with \qquad ||i|| = (bi, 0)$$

$$RTs_{bj} = ||S_j|| \qquad with \qquad ||j|| = (bj, 0),$$

$$RT_{(bi,i)} = ||S_{i'}|| \qquad with \qquad ||i'|| = (bi, i)$$

$$RT_{(bi,j)} = ||S_{j'}|| \qquad with \qquad ||j'|| = (bj, j).$$

After we established that the translation into DEX instructions in the form of blocks preserves typability, we also need ensure that the next phases in the translation process also preserves typability. The next phases are ordering the blocks, output the DEX code, then fix the branching targets.

**Lemma VII.8.** Let ||P|| be typable basic blocks resulting from translation of JVM instructions still in the block form, i.e.

$$||P||$$

= Translate(TraceParentChild(StartBlock(P))).

Given the ordering scheme to output the block contained in  $\mathbf{PickOrder}$ , if the starting block starts with flag 0 ( $F_{(0,0)} = 0$ ) then the output [P] is also typable.

Finally, the main result of this paper in that the compilation of typable JVM bytecode will yield typable DEX bytecode which can be proved from Lemma VII.7 and Lemma VII.8. Typable DEX bytecode will also have the non-interferent property because it is based on a safe CDR (Lemma VII.1) according to DEX.

**Theorem VII.1.** Let P be a typable JVM bytecode according to its safe CDR (region, jun), PA-Analysis (classAnalysis and excAnalysis), and method policies  $\Gamma$ , then  $\llbracket P \rrbracket$  according to the translation scheme has the property that